ISSN: 2454-7875

**VOLUME 2, ISSUE 10, Oct. -2016**

# A NOVEL MODIFIED CASCADED MULTILEVEL INVERTER WITH OPTIMAL NUMBER OF CONSTANT ACTIVE SWITCHES

#### PALAKURTHI N V S AYYAPPA

Dept. of Electrical Engineering University Visvesvaraya College of Engineering Bengaluru, India ayyappauvce@gmail.com

# MANJUNATHA Y R

Dept. of Electrical Engineering

University Visvesvaraya College of Engineering

Bengaluru, India yrm\_uvce\_ee@bub.ernet.in

#### ABSTRACT:

As of late utilization of multilevel inverters (MLI) are expanded for high power mechanical applications. This paper introduces a changed cascaded MLI for 31-levels utilizing optimal number of constant active switches at any given purpose of time. The circuit comprises of arrangement associated sub cell which are utilized to deliver positive levels. H-extension is further associated with circuit to create alternative waveform. Power supply of this circuit is in binary arrangement Voltage balancing issue is comprehended by utilizing this setup. Selective Harmonic Elimination is utilized to ascertain the switching pulses for **MATLAB/SIMULINK** tilized logical investigation of the circuit.

KEYWORDS: Sub cell, asymmetric supply, binary configuration, optimal number of constant active switches, voltage balancing

#### INTRODUCTION

Presently a day's multilevel inverter assumes an essential part in numerous mechanical and high power applications. It has the preferences like low dv/dt and di/dt stress over the switch and low EMI is watched. It utilizes different low voltage sources to create high voltage yield. This component gives the application in renewable vitality sources like sun based and energy units. They got yield waveform from MLI is almost sinusoidal which has better power quality.

Cascaded H-Bridge inverter is fundamental multilevel inverter which has points of interest like measured quality, low push over the switches, quality yield waveforms. Be that as it may, it needs more number of switches; misfortunes are high, size, and cost of the circuit more. It has the voltage balancing issue because of more number of switches.

This paper presents adjusted cascaded MLI. It comprises of various sub cells by which it can deliver positive levels, further H-bridge is utilized to create the positive and negative half cycles. This has the benefit of optimal number of constant active switches at any given purpose of time. The circuit is supplied with unsymmetrical voltage sources which are in binary design. This can take care of the voltage balance issue present in Cascaded H-Bridge MLI.

# LITERATURE REVIEW:

Multilevel inverters are considered today as a attractive solution for medium-voltage, high power applications. In fact several major manufacturers commercialize Neutral Point Clamped (NPC), Flying capacitor (FC) or Cascaded H-Bridge (CHB) topologies with a wide variety of control methods [1]. Multilevel inverters have the advantage of low dv/dt and low di/dt during switching. The quality of output is improved and having low THD.

The voltage sources can be configured in different ratios, sources may be symmetrical or asymmetrical. In symmetrical all sources values will be same. In asymmetrical configuration sources may be in binary or trinary configuration. This gives the advantage of having more voltage levels with less number of sources. Another advantage of asymmetrical configuration is we obtain less THD values [2, 3]. In CHB configuration, due to more number of switches, charge unbalance problem may occur; this problem can be resolved by using duty cycle swapping method [4]

Different topologies have been proposed with reduced number of switches [5, 6]. In symmetrical configuration the topology needs more number of switches, with this the efficiency decreases, complexity and cost of the system increases. With asymmetrical configuration we can overcome these problems.

**VOLUME 2, ISSUE 10, Oct. -2016**

The control signals to switches can be given by using different modulation techniques [7] such as Fundamental Frequency Switching, Multicarrier Pulse Width Modulation, and Space Vector Modulation. Fundamental frequency switching has the advantage of less switching losses.

# PROPOSED MODIFIED CASCADED MULTILEVEL INVERTER:

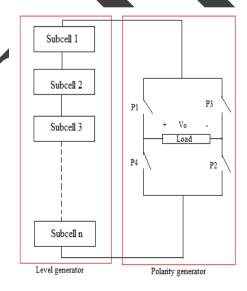

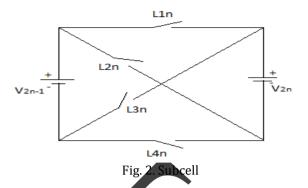

The modified cascaded MLI is as appeared in Fig 1. As appeared in figure it comprises various sub cells. All sub cells are associated as appeared in the Fig 1. Each sub cell is as appeared in Fig 2. Each sub cell comprises of two voltage sources. The voltage source can be a renewable vitality sources like nearby planetary group, energy units or any capacity gadgets like batteries, capacitors. Every cell comprises of four switches in that two switches  $L_{2n}$  and  $L_{3n}$  are unidirectional switches.  $L_{1n}$ and L<sub>4n</sub> are bidirectional changes which need to with stand with both positive and negative voltages. With the utilization of inductive burdens reverse streams may happens with that the changes need to withstand. With the assistance of cascaded sub cells it can create positive levels. H-extension is associated with it to produce both positive and negative polarities, P<sub>1</sub> and P<sub>2</sub> will lead amid positive half cycle P3 and P4 will direct amid negative half cycle. More number of steps can be acquired. Because of this it can create about sinusoidal waveform which enhances the power quality. The configuration procedure is examined in further segments. The switching table is as given in Table 1. For positive yield levels in that P<sub>1</sub> and P<sub>2</sub> are on for negative yield levels P<sub>3</sub> and P4 will direct. From the switching table we can watch that the quantity of directing switches are same at moment of time.

Fig. 1. Modified cascaded multilevel inverter

Table 1 Switching states of binary configuration

|   | L1 | L2 | L3 | 14 | M  | L2 | L3 | L4 | Lev |

|---|----|----|----|----|----|----|----|----|-----|

|   | 0  | 0  | 1  | 0  | 9  | 0  | 1  | 0  | 0   |

|   | 1  | 9  | 0  | 0  | 0  | 0  | 1  | 0  | 1   |

|   | 0  | 0  | 0  | 1  | 0  | 6  | 7  |    | 2   |

| 4 | 0  | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 3   |

|   | 0  | 0  | 1  | 0  | .1 | 0  | 0  | 0  | 4   |

|   | 1  | 0  | 0  | 0  | ¥  | 0  | 0  | 0  | 5   |

|   | 0  | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 6   |

|   | 0  | 1  | 0  | 0  | 7  | 0  | 0  | 0  | 7   |

|   | 0  | 0  | 1  | 9  | 0  | 0  | 0  | 1  | 8   |

|   | 1  | 0  | 9  | 0  | 0  | 0  | 0  | 1  | 9   |

|   | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 10  |

|   | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 11  |

|   | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 12  |

|   | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 13  |

|   | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 14  |

|   | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 15  |

#### **DESIGN OF MODIFIED CASCADED MLI:**

The proposed circuit requires 2k+4 switches for the given k DC voltage sources. The following (1) gives the relation between number of DC voltage sources and sub cells

$$n=k/2 \tag{1}$$

$$N_{sw}=2k+4$$

(2)

In symmetrical configuration all voltage sources are equal

$$V_1 = V_2 = V_3 = \dots = V_n$$

(3)

In the proposed topology the voltage sources  $V_1$ ,  $V_2$ ,  $V_3$  .......  $V_n$  relation in general given by the (4)

$$V_i = r^{m-1} V_{DC} \tag{4}$$

Where i=1,2,3,..., r is the ratio factor of the voltage sources in binary configuration r=2The total output voltage of the given topology is given by the (5)

$$V_{\text{out}} = {}^{+}_{-}(V_{01} + V_{02} + \cdots + V_{0n})$$

(5)

**VOLUME 2, ISSUE 10, Oct. -2016**

The maximum output voltage for a given voltage ratio factor given by the (6)

$$V_{out\ max} = \left(\frac{r^{k}-1}{r-1}\right) V_{DC} \tag{6}$$

The number of voltage levels that can be generated in general given by the (7)

$$N_{out\ level} = 2 * \left(\frac{r^{k}-1}{r-1}\right) + 1 \tag{7}$$

The reverse blocking voltage of nth basic sub cell given by the (8)

$$V_{b \text{ nth subcell}} = V_{b \text{ L1n}} + V_{b \text{ L2n}} + V_{b \text{ L3n}} + V_{b \text{ L4n}}$$

$$V_{b \text{ nth cell}} = 2V_{2n-1} + 4V_{2n}$$

(8)

The reverse blocking voltage of total circuit given by the (9)

$$V_{b \ circuit} = \sum_{i=1}^{n} (2V_{2i-1} + 4V_{2i})$$

(9)

## A. Snubber Circuit Design

Turnoff snubber arrangement is used to obtain zero voltage across the switch when current goes to zero [8]. The value of snubber circuit elements are given by the (10) and (11)

$$R_{s} = 5 * \frac{V_{d}}{I_{0}}$$

$$(10)$$

$$C_{s} = \left(\frac{I_{0} * I_{f}}{2 * V_{d}}\right)$$

$$(11)$$

Where  $R_s$  is turnoff snubber resistor,  $C_s$  is turnoff snubber capacitor. C<sub>s</sub> is used to limit dy dt during switching.

### B. Total harmonic distortion:

The important performance factor for a inverter is total harmonic distortion (THD) [9]. For the sinusoidal waveform, the THD is defined as follows

$$THD = \sqrt{\frac{V_{0.7ms}}{V_{0.1}}^2 - 1}$$

(12)

Where  $V_{0.7ms}$  represents the rms magnitude of the

output voltage. In the above relation, the values of  $V_{\rm 01}$ and V<sub>orms</sub> can be obtained using the following equations respective

$$V_{otms} = \frac{2\sqrt{2}V}{\pi} * \sqrt{\sum_{m=1,3,5,\dots,n}^{\infty} \left(\sum_{j=1}^{N_{level}} \frac{\cos(m\theta_j)}{m}\right)^{\frac{1}{2}}}$$

$$V_{01} = \frac{2\sqrt{2}V}{\pi} * \sqrt{\sum_{j=1}^{N_{level}} \cos(\theta_j)}$$

(13)

Where the values of  $\theta_1, \theta_2, \theta_3, \dots \dots, \theta_{N \ level}$ represents switching angles are obtained by (15) for the given values j=1, 2, 3, ...... $N_{le}$   $\theta_j = \sin^{-1} \left( \frac{1 - 0.5}{N_{level}} \right)$

$$\theta_j = \sin^{-1} \left( \frac{j - 0.5}{N_{level}} \right) \tag{15}$$

#### **SIMULATION RESULTS:**

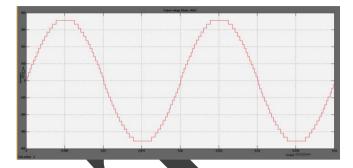

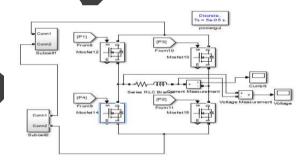

The proposed topology is simulated using MATLAB/SIMULINK. The DC voltages used are V<sub>1</sub>=24v, V<sub>2</sub>=48v, V<sub>3</sub>=96v, V<sub>4</sub>=192v. Various output voltage levels are generated as per switching table 1. Switches P<sub>1</sub>, P<sub>2</sub> are used to produce positive half cycle, switches P<sub>3</sub>, P<sub>4</sub> are on for complimentary half cycle i.e for negative half cycle. Simulation was done for RL load with values 40ohm, 40mH. Frequency of output voltage is 50HZ. Switching pulses are given to MOSFETS by Selective Harmonic Elimination method. Simulation diagram is as shown in the Fig. 3.

Fig. 3. Simulation diagram

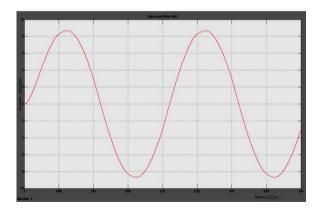

Fig. 4 and Fig. 5. shows the 31 level modified scaded MLI simulated output voltage waveform and utput current waveform respectively for RL load with the values 40ohm, 40mH. Current waveform is close to sinusoidal waveform even without using the passive filters. It is also clear that there is phase difference between voltage and current waveforms.

Fig. 4. Simulated output voltage waveform of 31-level inverter

Fig. 5. Simulated output current waveform of 31-level inverter

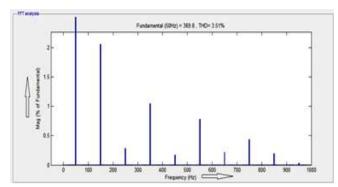

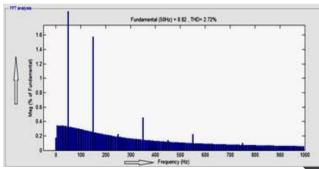

Fig. 6. shows the FFT analysis of the 31 level MLI output voltage waveform. The THD value is 3.51%. Fig. 7.

**VOLUME 2, ISSUE 10, Oct. -2016**

shows the FFT analysis of the 31 level MLI output current waveform. The obtained THD value is 2.72%. Obtained THD values are less than IEEE standards (i.e < 5%) without using passive filter.

Fig. 6. FFT analysis of simulated output voltage waveform

Fig. 7. FFT analysis of simulated output current waveform

#### **CONCLUSION:**

The proposed modified cascaded MLI utilizes constant active number of switches. Yield waveform quality is acquired with the high number of levels. They got THD of voltage waveform is 3.51%, PHD of current waveform is 2.72% which are less than IEEE standard (i.e < 5%) without utilizing detached channel. The upside of this topology is

- Circuit is basic and secluded.

- Used ideal steady number of dynamic switches.

- Voltage unbalancing issue dispensed with.

The productivity of the circuit is enhanced with the utilization ideal number of switches and gate drivers, which in-turn lessens the size cost and control manysided quality of the circuit

#### **REFERENCES:**

- 1) L. G. Franquelo; J.Rodriguez, J. I. Leon, S. Kouro, R. Portillo, and M. A. M. Parts, "The age of multilevel converters arrives," IEEE Ind. Electron. Mag., Vol.2, no. 2, pp.28-39, Jun. 2008.

- 2) Kiruthika. P, Ramani. K, "Design of Hybrid Multi-level Inverter with Minimum Number of switches Interface with Photo voltaic," IEEE conference on Electronics and Communication System 2015.

- 3) O. L. Jimenez, R. A. Vargas, J. Aguayo, J. E. Arau, G. Vela, A. Claudio, "THD in Cascade Multilevel Inverters Symmetric and Asymmetric," IEEE conference on Electronics, Robotics and Automotive Mechanics 2011.

- 4) Leon M.Tolbert, Fang Zheng peng, Tim Cunnyngham, John N. Chiasson, "Charge Balance Control Schemes for Cascade Multilevel Conveter in Hybrid Electric Vehicles," IEEE transaction on Industrial Electronics, vol. 49, No. 5, October 2002

- 5) Krishna Kumar Guptha, Alekh Ranjan, Pallvee Bhatnagar, Lalit Kumar Sahu, "Multilevel Inverter Topologies with Reduced Device Count: A Review," IEEE transactions on Power Electronics. Vol. 31, No. 1, Jan 2016

- 6) Mohd Wajahatullah Naseem, Amit Mohod, "A Novel Multilevel Inverter with Reduced Count of Power Switches," JEEE transactions 2015

- Dr(Mrs).Hina B. Chandwani, Mrs. Meeta K. Matnani,

"A Review of Modulation Techniques for Hybrid

Multilevel Inverter," IEEE International Conference

on Emerging Technology Trends in Electronics,

Communication and Networking 2012

- 8) Jamal Al-Nasseri, Christian Weindl, Gerhard Herold, Joerg Flotthmesh, "A Dual-use Snubber Design for Multi-level Inverter Systems," IEEE transactions 2006

- 9) Rasoul Shalchi Alishah, Daryoosh Nazarpour, Seyyed Hossein Hoseeini, Mehran Sabahi, "New hybrid structure for multilevel inverter with fewer number of components for high-voltage levels" IET Power Electron., 2014, vol. 7, Iss. 1, pp. 96-104