ISSN: 2454-7875

VOLUME 2, ISSUE 9, Sep. -2016

# THREE-LEVEL INVERTER CONTROLLED BY MEANS OF HYSTERESIS CURRENT CONTROL. APPLICATION TO GRID INTEGRATION

CHAITRALI S. SHEDGE

M. Tech. Electrical, Department of Electrical Engineering Dr. Babasaheb Ambedkar Technological University, Lonere-402103.

# RAJENDRA H. MADHAVI

Professor of Electrical Engineering, Department of Electrical Engineering Dr. Babasaheb Ambedkar Technological University, Lonere-402103.

#### ABSTRACT:

This paper describes the operational analysis results of a grid integration of distributed generation sources with an AC grid using multilevel inverter. The multilevel inverter is a three-level voltage source inverter (VSI), which is controlled by means of a novel vector hysteresis current control (V.H.C.C). The proposed V.H.C.C, which is based on error square areas, controls the three-phase load AC currents. The three load current errors are gathered into a single space vector quantity. In this case, the magnitude of the error vector is limited within boundary areas of a square shape. The control scheme is based on the detection of areas and sectors, in which the vector tip of the current error can be located. Then it applies an appropriate voltage vector among the 27 voltage vectors. Inherent advantages of current hysteresis controller are retained with the added advantage of adjacent voltage vector selection for hysteresis PWM control. Simple look-up tables are required for the detection of areas and sectors, and also for the vector selection. A detailed model of wind power generation, photo-voltaic generation and multilevel inverter with its current controlled SVPWM technique was implemented with a MATLAB.

KEY WORDS: Space vector PWM, Simulink model, Distributed generation sources.

#### INTRODUCTION:

The DG sources consist of PV cell, wind power generator that behaves as coordinated entity. As most of the DG unit are interfaced to the grid using power electronics converter, they have opportunity to realize enhance power generation to flexible digital control of the power converter. This system is interconnected with medium voltage AC grid via DC to AC multilevel inverter. Multilevel inverter technologies are increasingly gaining attention due to the advantages of utilization in medium and high power applications, improving the quality of

voltage waveform and reducing stress across the inverter switches. The most commonly used multilevel topology is the diode clamped inverter, in which the diode is used as the clamping device to clamp the dc bus voltage so as to achieve steps in the output voltage. The principle of diode clamping to DC-link voltages can be extended to any number of voltage levels. The most pepular control techniques for multilevel inverter are well known; carrier based modulation and space vector modulation SVM.

The previous schemes are based on voltage control. They are widely used for an open loop control system due to their operation at fixed frequency. However the control strategies based on current control appear as a good choice to control the inverter currents for the closed loop control system. The proposed control scheme gathers three phase current into a single space vector quantity. In this case the magnitude of the error vector is fimited within boundary areas of a square shape.

# WORK OBJECTIVE:

The main objective of this work is to contribute to the topic of inverter modeling and controlled by developing an accurate control technique of current controlled space vector PWM and based on this model contemplate the control issues. The scientific objective of this research include the following.

- 1. Modeling and dynamic behavior of investigation of multilevel inverter and current controlled SV-PWM technique.

- 2. Simulation of the overall DG system integrated with the grid using multilevel inverter.

## **SYSTEM DESCRIPTION:**

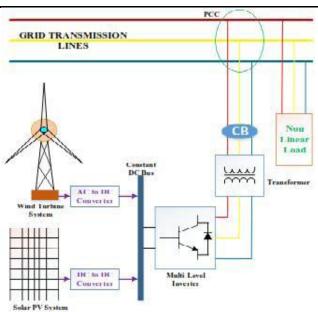

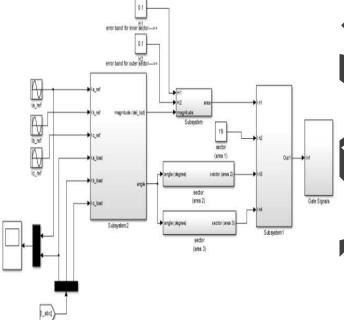

As shows in fig.1 the proposed system consist of DG's such as wind power and photo-voltaic generation, grid tied DC/AC multilevel inverter ,an interface and a Hysteresis Current Controller (H.C.C.) based space vector PWM technique.

VOLUME 2, ISSUE 9, Sep. -2016

THE PROPOSED VECTOR HYSTERESIS CURRENT

CONTROL:

1. PRINCIPLE OF SPACE VECTOR PWM:

• Treats the sinusoidal voltage as a constant amplitude vector rotating at constant frequency.

• This PWM technique approximates the reference voltage

Vref by a combination of the 27 switching patterns (V0 to V26).

2. COORDINATE TRANSFORMATION (abc reference frame to the stationary d-q frame):

A three-phase voltage vector is transformed into a vector in the stationary d-q coordinate frame which represents the spatial vector sum of the three-phase voltage.

# 3. CURRENT-CONTROLLED PWM:

urrent-controlled PWM (CC-PWM) inverters considerable advantages compared conventional voltage controlled PWM voltage source nverters (VSIs). Different ways of classification of urrent controllers can be found in, amongst which the hysteresis controllers are widely used because of their inherent simplicity and fast dynamic response. However, ome of the drawbacks of conventional type of hysteresis controller, e.g. limit cycle oscillations, overshoot in current error, generation of sub-harmonic components in the current ar a random (non-optimum) switching are very well known. Current-error space-vector-based hysteresis controllers allow the current-error space ector to move within a specified boundary. Hexagonal, circular and rectangular shapes of current-error space ector boundary are reported in the literature.

Figure 1.Grid Integration of the DG's with ac Grid using multilevel inverter.

#### **MULTILEVEL INVERTER:**

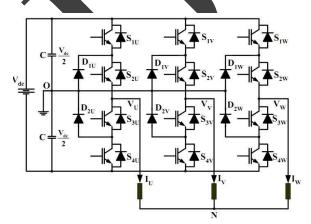

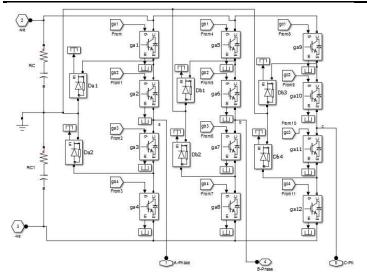

The most commonly used multilevel topology is the diode clamped inverter, in which the diode is used as the clamping device to clamp the dc bus voltage so as to achieve steps in the output voltage. The principle of diode clamping to DC-link voltages can be extended to any number of voltage levels. Since the voltages across the semiconductor switches are limited by conduction of the diodes connected to the various DC levels. DCMLI works on the concept of using diodes to limit voltage stress on power devices. A DCMLI typically consists of (m-1) capacitors on the DC bus. Figure.2 shows the circuit for a diode clamped three phase, three-level inverter.

The diode clamped inverter provides multiple voltage levels through connection of the phases to a series of capacitors.

Figure 2. Diode clamped three phase, three-level inverter.

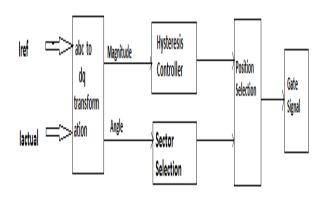

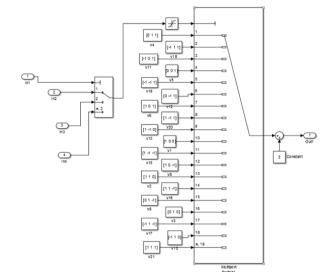

Figure 3. Current Controlled SVPWM technique

# AREAS AND DETECTION OF SECTORS:

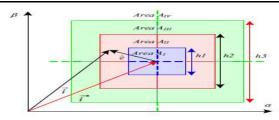

The basic idea of the proposed V.H.C.C is to keep the measured load currents within their hysteresis boundaries in real time. These currents are transformed into  $(\alpha,\beta)$  coordinate frame. With the transformation of the three hysteresis bands into this coordinate system, they result in four hysteresis square areas.

VOLUME 2, ISSUE 9, Sep. -2016

Figure 4.Error vector tip location in the four possible area.

The reference current and the measured load current can be both expressed using the space vector representation as:

$i_{ref} = i_{aref} + i_{bref} + i_{cref}$   $i_{load} = i_a + i_b + i_c$

By the same way, the error vector is defined by  $e = i_{ref}$ - $i_{load}$  and can be expressed in  $(\alpha,\beta)$  reference frame by the following expression:  $e=e_{\alpha}+e_{\beta}$

The tip of the reference current vector  $i_{ref}$  is located in the center of area AI. The tip of the measured current vector I can be located in one of the four areas (AI, AII, AIII and AIV), according to the three hysteresis bands h1,h2, h3 and x > h3, as it is illustrated in figure 4. The choice of four areas is taken to use the four categories of voltage vectors; zero, small, medium and large.

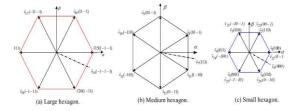

# SELECTION OF THE APPROPRIATE VOLTAGE VECTOR:

Regardless to the three zero voltage vectors (ZVV) (v0,v7,v14), the 24 active voltage vectors (AVV) of the three level VSI are divided into three categories large, medium and small. One among the three (ZVV) (v0,v7,v14) is applied when the error vector tip is located in area AI. In the case where the error vector tip is located in area AII, one of the small voltage vectors will be applied. By the same way, if the error vector tip is located in area AIII, one of the medium voltage vectors will be selected.

Otherwise, one of the large voltage vectors will be applied when the error vector tip is located in area AIV (outside areas AI, AII and AIII). To reduce the switching frequency of the inverter switches, the ZVV must be applied. This will be carried out only when it is certain that the action of the inverter voltage vector has the natural tendency to push the error vector tip towards the hysteresis boundary areas.

Figure 5.Three level voltage inverter vector in  $(\alpha,\beta)$  plane

There are totally 24 minor sectors in the plane. And the vertices of these sectors represent the voltage vectors as shown in table 1. In three-phase three-level inverter, when the rotating voltage vectors falls into one certain sector, adjacent voltage vectors are selected to synthesize the desired rotating voltage vector based on the vector synthesis principle, resulting in three-phase PWM waveforms.

Table 1. Selection of voltage vector

|   | Switching states | S <sub>a</sub> S <sub>b</sub> S <sub>c</sub> | Voltage vector  |

|---|------------------|----------------------------------------------|-----------------|

|   | $S_1$            | 000                                          | $V_0$           |

|   | S <sub>2</sub>   | 100                                          | $V_1$           |

|   | S <sub>3</sub>   | 110                                          | V <sub>2</sub>  |

| 4 | S4               | 010                                          | V <sub>3</sub>  |

|   | S <sub>5</sub>   | 011                                          | V               |

|   | S <sub>6</sub>   | 0 0 1                                        | V <sub>5</sub>  |

|   | S <sub>7</sub>   | 101                                          | V <sub>6</sub>  |

|   | S <sub>8</sub>   | 1.1                                          | V <sub>7</sub>  |

|   | S <sub>9</sub>   | 10-1                                         | V <sub>8</sub>  |

|   | S <sub>10</sub>  | 11-1                                         | $V_9$           |

|   | S <sub>11</sub>  | -1 1 0                                       | V <sub>10</sub> |

|   | S <sub>12</sub>  | -1 0 1                                       | V <sub>11</sub> |

|   | S <sub>13</sub>  | 0 -1 1                                       | V <sub>12</sub> |

|   | S <sub>14</sub>  | 1 -1 0                                       | V <sub>13</sub> |

|   | S <sub>15</sub>  | -1 -1 -1                                     | V <sub>14</sub> |

|   | S <sub>16</sub>  | 1 -1 -1                                      | V <sub>15</sub> |

|   | S <sub>17</sub>  | 11-1                                         | V <sub>16</sub> |

|   | S <sub>18</sub>  | -1 1 -1                                      | V <sub>17</sub> |

|   | S <sub>19</sub>  | -111                                         | V <sub>18</sub> |

|   | S <sub>20</sub>  | -1 -1 1                                      | V <sub>19</sub> |

|   | S <sub>21</sub>  | 1-11                                         | V <sub>20</sub> |

|   | S <sub>22</sub>  | 0 -1 -1                                      | V <sub>21</sub> |

|   | S <sub>23</sub>  | 0 0-1                                        | V <sub>22</sub> |

|   | S <sub>24</sub>  | -1 0 -1                                      | V <sub>23</sub> |

|   | S <sub>25</sub>  | -1 0 0                                       | V <sub>24</sub> |

|   | S <sub>26</sub>  | -1 -1 0                                      | V <sub>25</sub> |

|   | S <sub>27</sub>  | 0 -1 0                                       | V <sub>26</sub> |

|   |                  |                                              |                 |

Figure 6. Simulation Model of Three Phase three level diode clamp Inverter.

Figure 8. Simulation Model of Inverter Switching States.

Figure 8. Simulation Model of Hysteresis Control

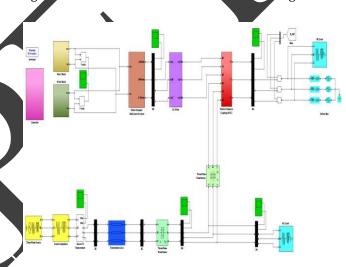

Figure 9. Simulation Model of overall system

### **CONCLUSION:**

This paper has presented the simulation results of a novel vector hysteresis current control based on error square areas applied on three-level VSI. The proposed control technique for the three-level VSI gathers the three current errors into a single space vector quantity avoiding by that the phase current interactions in the three phase system. Moreover, the application of the three zero voltage vectors reduces considerably the switching frequency.

#### REFERENCES:

- 1) D. Sandhya Rani, A.Appaprao, "A Space Vector PWM Scheme for Three level Inverters Based on Two-Level Space Vector PWM", (IJPSOEM) Volume-1, Issue-1, 2011

- 2) B. Chitti Babu, Bathula Vasantha Reddy, "An Improved Dynamic Response of Voltage Source Inverter using Novel Hysteresis Dead Band Current

VOLUME 2, ISSUE 9, Sep. -2016

- *Controller*", 18th annual symposium on emerging needs in computing, communication, signals and power- 2009, 29th august, 2009

- 3) B.Vasantha Reddy, B.Chitti Babu, "Hysteresis Controller and Delta Modulator- Two Viable Schemes for Current Controlled Voltage Source Inverter", IEEE ICOTP 2009,14-15/Dec/2009.

- 4) Mohamayee Mohapatra, B.Chitti Babu, "Fixed and Sinusoidal-Band Hysteresis Current Controller for PWM Voltage Source Inverter with LC Filter", IEEE Student's Technology Symposium 2010,IIT Kharagpur,03-04/April/2010.

- 5) A. Chatterjee, K. B. Mohanty, "Design and Analysis of Stationary Frame PR Current Controller for Performance Improvement of Grid Tied PV Inverters".

- 6) Satyaranjan Jena, B. Chitti Babu, S. R. Samantaray and Mohamayee Mohapatra, "Comparative Study Between Adaptive Hysteresis and SVPWM Current Control for Grid-connected Inverter System",14-16/Jan/2011.

- 7) Lavanya Komma, Rangavalli Vasa, "Simulation and Comparison of Three Level Inverter Using SVPWM & SPWM", International Journal of Electrical and Electronics Research ISSN 2348-6988 (online) Vol. 2, Issue 3, pp: (21-30), Month: July September 2014.

- 8) Marcelo Gradella Villalva, Ernesto Ruppert Filho, "Current Controller with 3-D SVPWM for 3-Phase 4-Wire Active Filters", 13083-852 Campinas SP.

- 9) Anubrata Dey, P. P. Rajeevan, Rijil Ramchand, K. Mathew, and K. Gopakumar, "A Space-Vector-Based Hysteresis Current Controller for a General n-Level Inverter-Fed Drive With Nearly Constant Switching Frequency Control", IEEE transactions on industrial electronics, vol. 60, no. 5, may 2013.

- 10) T. Ghennam, E. M. Berkouk, B. François, "Three-level Inverter Controlled by means of Vector Hysteresis Current Control. Application to Back to Back Structure", 1-4244-0755-9/07/\$20.00 '2007 IEEE.

- 11) P.N. Tekwani, R.S. Kanchan and K. Gopakumar, "Current-error space-vector-based hysteresis PWM controller for three-level voltage source inverter fed drives", IEE Proc.-Electr. Power Appl., Vol. 152, No. 5, September 2005

- 12) BOR-REN LIN, HSIN-HUNG LU, "Single-Phase Power-Factor-Correction AC/DC Converters with Three PWM Control Schemes", IEEE transactions on aerospace and electronic systems vol. 36, no. 1 january 2000.

- 13) Marian P. Kazmierkowski and Waldemar Sulkowski, "A Novel Vector Control Scheme for Transistor PWM Inverter-Fed Induction Motor

- *Drive"*, IEEE transactions on industrial electronics, vol. 38, no. 1, february 1991

- 14) Yasser Abdel-Rady Ibrahim Mohamed and Ehab F. El-Saadany, "An Improved Deadbeat Current Control Scheme With a Novel Adaptive Self-Tuning Load Model for a Three-Phase PWM Voltage-Source Inverter", IEEE transactions on industrial electronics, vol. 54, no. 2, april 2007.

- 15) P. Enjeti, J.F. Lindsay, P.D. Ziogas, M.H. Rashid, "New current control scheme for PWM inverters", IEE proceedings, vol. 135, pt. b, no. 4, july 1988.

- 16) Anand Sathyan, Nikola Milivojevic, Young-Joo Lee, Krishnamurthy, and Ali Emadi, "An FPGA-Based Novel Digital PWM Control Scheme for BLDC Motor Drives", IREE transactions on industrial electronics, vol. 56, no. 8, august 2009.