# MODEL DAN SIMULASI PERBANDINGAN PROTOTYPE RANGKAIAN DIGITAL HALF ADDER ALU STANDAR DENGAN INOVASI RANGKAIAN DIGITAL HALF ADDER ALU

Helmi Fauzi Siregar <sup>1</sup>, Muhammad Dedi Irawan <sup>2</sup>

\*1,2 Program Studi Teknik Informatika, Universitas Asahan,

Jl. Jend. Ahmad Yani Kisaran 21244, Sumatera Utara, Telp: (0623) 347222

fauzi.helmi.hf@gmail.com<sup>1</sup>, temansejati.dedi@gmail.com<sup>2</sup>

Abstrak - Penelitian ini dilakukan untuk membuat model dan simulasi sistem Half Adder. Sistem ini dirancang dengan melakukan analisa dengan metode deskriptif, dan metode komperatif. Setelah dilakukan analisa, maka dilakukan pemodelan dengan UML (Unified Modelling Language) dan dilakukan perancangan hardware berbasis microcontroller yang dapat diprogram dengan menggunakan software CodeVisionAVR-C. Hasil penelitian ini adalah sebuah prototype sistem Half Adder ALU standar yang menggunakan gerbang XOR, AND, OR dengan Inovasi sistem Half Adder ALU menggunakan Gerbang NAND dan NOR.

Kata Kunci - Half Adder, Prototype, XOR, AND, OR, NAND, NOR

Abstract - This research was conducted to model and simulate the Half Adder system. This system is designed by analyzing the descriptive method, and the comparative method. After analysis, modeling is done with UML (Unified Modeling Language) and hardware design based on microcontroller can be programmed using CodeVisionAVR-C software. The results of this study are a standard prototype Half ALU ALTER Adder system that uses XOR, AND, OR gates with ALU Half Adder system innovation using NAND and NOR gates. Keywords - Half Adder, Prototype, XOR, AND, OR, NAND, NOR

#### I. PENDAHULUAN

Rangkaian digital adalah matakuliah yang ada di setiap perguruan tinggi baik swasta maupun negeri. Pada matakuliah rangkaian digital mahasiswa dituntut untuk memahami bagaimana proses data analog menjadi data yang digital. Kemudian mahasiswa diharapkan memahami bagaimana proses data-data yang diolah oleh processor baik data yang berbentuk matematik ataupun data yang berbentuk huruf dan simbol-simbol.

Pada rangkaian digital dipelajari tentang karakteristik pada ALU Pada rangkaian half adder ini digunakan gerbang logika EX-OR dan AND untuk melakukan penjumlahan dua buah binary digit sehingga menghasilkan satu buah binary digit dan satu buah binary digit carry of. Sedangkan pada rangkaian full adder ini menggunakan dua buah gerbang logika EX-OR, tiga buah gerbang logika AND, dan satu buah gerbang logika OR.

Penulis ingin membahas pada penelitian ini, yaitu pada rangkaian *adder* tersebut. Dimana rangkaian *adder* yang telah dijelaskan diatas merupakan rangkaian *adder* yang standar yang akan penulis bandingkan pada rangkaian *adder* yaitu rangkaian *half adder* yang menggunakan gerbang logika *NOR* dan *NAND*. Sedangkan pada rangkaian *full adder* yang digunakan adalah rangkaian full adder standar.

Penulis ingin menyajikan pada penelitian ini dalam bentuk *prototype* untuk menjadi alat yang dapat membantu memahami unit aritmatika di dalam melakukan pengolahan data

matematis. Kemudian yang ingin penulis ungkap pada penelitian ini adalah bahwa rangkaian

half adder yang standar bisa digantikan dengan rangkaian half adder yang di kembangkan dengan menggunakan gerbang NOR dan NAND yang akan menghasilkan bilangan binary digit yang sama seperti rangkaian half adder yang standar.

Dari permasalahan diatas, maka penulis mengambil sebuah judul penelitian yaitu "Model Dan Simulasi Perbandingan Prototype Rangkaian Half Adder ALU Standar Dengan Inovasi Rangkaian Digital Half Adder ALU".

#### A. Rumusan Masalah

- Rumusan masalah dari penelitian ini adalah sebagai berikut :

- 1. Bagaimana Rangkaian *Adder* menyelesaikan operasi penjumlahan pada bilangan biner?

- Bagaimana hasil perbandingan antara rangkaian adder standar dengan rangkaian adder yang menggunakan gerbang logika NAND dan NOR?

## B. Batasan Masalah

Batasan masalah yang digunakan dalam penelitian ini adalah :

- 1. Penelitian ini hanya membahas proses penjumlahan *binary digit* pada *prototype*Rangkaian *Adder*.

- 2. Proses penjumlahan dan hasil penjumlahan akan ditampilkan pada LCD

- 3. Rangkaian *Adder* yang dibahas adalah rangkaian *half adder* dan *full adder*.

- C. Tujuan Penelitian

- Tujuan dari penelitian ini adalah:

- 1. Membuat dan menerapkan model *prototype* untuk alat praktek di dalam memahami proses penjumlahan *binary digit*.

- 2. Mengevaluasi rangkaian *adder* yang standar dengan rangkaian *adder* yang menggunakan gerbang logika *NAND* dan *NOR*.

- 3. Membuat alat simulasi berupa *prototype* di dalam mempraktekkan penjumlah bilangan *binary digit*.

# D. Manfaat Penelitian

Adapun manfaat dari penelitian ini adalah:

- 1. Dapat memberikan hasil secara cepat, tepat, dan akurat dalam melakukan perhitungan penjumlahan bilangan *binary digit*.

- 2. Dapat membantu mahasiswa dikalangan perguruan tinggi swasta maupun negeri dalam memahami proses penjumlahan yang dilakukan komputer.

#### II. LANDASAN TEORI

#### A. Adder

Penjumlah atau *Adder* adalah komponen elektronika digital yang dipakai untuk menjumlahkan dua buah angka dalam sistem bilangan biner. Dalam komputer dan mikroprosesor, *Adder* biasanya berada di bagian ALU (*Arithmatic Logic Unit*). Sistem bilangan yang dipakai dalam proses penjumlahan, selain bilangan biner, juga 2's complement untuk bilangan negatif, bilangan BCD (*binary-coded decimal*), dan excess-3. Jika sistem bilangan yang dipakai adalah 2's complement, maka proses operasi penjumlahan dan operasi pengurangan akan sangat mudah dilakukan (Mathius Nugroho, 2015).

Berdasarkan penggunaannya, Adder dibagi menjadi 2 yaitu :

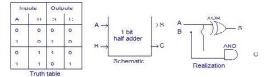

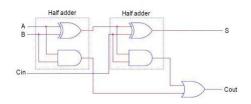

## 1. Half Adder

Half adder merupakan salah satu dari dua rangkaian adder yang menjumlahkan dua buah bit input, dan menghasilkan nilai jumlahan (sum) dan nilai lebihnya (carry-out). Half Adder diletakkan sebagai penjumlah dari bit-bit terendah (Least Significant Bit). Ketika salah satu atau lebih input bernilai nol maka keluaran pada gerbang AND pertama akan bernilai satu. Karenanya kemudian input di gerbang kedua dan ketiga akan bernilai satu dan mendapat input lain yang salah satunya bernilai nol sehingga PASTI gerbang AND yang masukannya nol tadi menghasilkan nilai satu. Sedangkan gerbang lain akan benilai nol karena mendapat input satu dan satu maka keluaran di gerbang AND terakhir akan bernilai satu, karena

salah satu inputnya bernilai nol.

Gambar 1 Tabel, Diagram, dan Simbol Half Adder

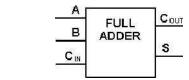

#### 2. Full Adder

Sebuah *full adder* menjumlahkan dua bilangan yang telah dikonversikan menjadi bilangan- bilangan biner. Masing-masing bit pada posisi yang sama saling dijumlahkan. *Full adder* sebagai penjumlah pada bit-bit selain yang terendah. *Full adder* menjumlahkan dua bit *input* ditambah dengan nilai *carry-out* dari penjumlahan bit sebelumnya. *Output* dari Full Adder adalah hasil penjumlahan (Sum) dan bit kelebihannya (carry-out). Blok diagram dari sebuah *full adder* diberikan pada gambar 2.2.

Gambar 2 Blok Diagram Rangkaian Full Adder

Gambar 3 Rangkaian Full adder

Keunggulan FULL*ADDER* bila dibandingkan dengan HALF ADDER adalah kemampuannya menampung dan menjumlahkan bit CARRY-in (Cin) yang berasal dari CARRY- out dari tahapan sebelumnya. penjumlahan dengan jumlah bit yang lebih banyak, dapat dilakukan dengan menambahkan rangkaian HALF ADDER, sesuai dengan jumlah bit input. Di pasaran, rangkaian FULL ADDER sudah ada yang berbentuk IC, seperti 74xx83 (4-bit FULL ADDER).

## B. Gerbang AND

Gerbang *AND* digunakan untuk menghasilkan logika 1 jika semua masukan berlogika 1, jika tidak maka *output* yang dihasilkan akan berlogika 0 (Kurniawan, Fredly, 2005). Simbol dan tabel kebenaran dari gerbang logika AND dapat dilihat berikut ini.

Gambar 4 Simbol Gerbang Logika AND

Tabel 1

Tabel Kebenaran dari Gerbang AND

| INPUT |   | OUTPUT |  |

|-------|---|--------|--|

| A     | В | Y      |  |

| 0     | O | O      |  |

| 0     | 1 | 0      |  |

| 1     | 0 | 0      |  |

| 1     | 1 | 1      |  |

Dari tabel kebenaran pada tabel 2.1 di atas, dapat diketahui bahwa *output* pada gerbang AND hanya akan berlogika 1 jika kedua inputnya berlogika 1

# C. Gerbang OR

Gerbang *OR* digunakan untuk menghasilkan logika 0 jika semua masukan berlogika 0, jika tidak maka *output* yang dihasilkan akan berlogika 1 (Kurniawan, Fredly, 2005). Simbol dan tabel kebenaran dari gerbang logika OR dapat dilihat berikut ini.

Gambar 5 Simbol Gerbang Logika OR

Tabel 2

Tabel Kebenaran dari Gerbang OR

| INPUT |   | OUTPUT |

|-------|---|--------|

| Λ     | В | Y      |

| 0     | 0 | 0      |

| 0     | 1 | 1      |

| 1     | 0 | 1.     |

| 1     | 1 | 1:     |

Dari tabel kebenaran pada tabel 2.2 di atas, dapat diketahui bahwa *output* pada gerbang OR hanya akan berlogika 0 jika kedua inputnya berlogika 0 dan jika tidak akan berlogika 1.

# D. Gerbang NOT

Gerbang NOT digunakan untuk menghasilkan logika yang kebalikan dari inputnya (Kurniawan, Fredly, 2005).

Gambar 6 Simbol Gerbang Logika NOT

Tabel 3

Tabel Kebenaran dari Gerbang NOT

| INPUT | OUTPUT       |  |

|-------|--------------|--|

| A     | $\mathbf{Y}$ |  |

| 0     | 1            |  |

| 1     | 0            |  |

Dari tabel kebenaran pada tabel 2.3 di atas, dapat diketahui bahwa *input* pada gerbang NOT menghasilkan *output* yang berlawanan dengan logika inputnya.

# E. Gerbang NOR

Gerbang NOR merupakan gerbang OR yang outputnya ditambah dengan gerbang NOT, digunakan untuk menghasilkan logika 1 jika semua masukan berlogika 1, jika tidak

maka *output* yang dihasilkan akan berlogika 0 (Kurniawan, Fredly, 2005). simbol dan tabel kebenaran dari gerbang logika AND dapat dilihat dibawah ini.

Gambar 7 Simbol Gerbang Logika NOR Tabel 4 Tabel Kebenaran dari Gerbang NOR

| INPUT |   | OUTPUT |  |

|-------|---|--------|--|

| A     | В | Y      |  |

| 0     | 0 | 1      |  |

| 0     | 1 | 0      |  |

| 1     | 0 | 0      |  |

| 1     | 1 | 0      |  |

Dari tabel kebenaran pada tabel 2.4 di atas, dapat diketahui bahwa *output* pada gerbang NOR hanya akan berlogika 1 jika kedua inputnya berlogika 0.

# III. METODOLOGI PENELITIAN

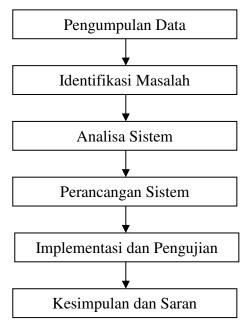

#### A. Kerangka Kerja Penelitian

Pada bab ini akan dijelaskan dan diuraikan mengenai kerangka kerja penelitian yang digunakan dalam penyelesaian penelitian ini. Kerangka kerja ini merupakan langkah-langkah yang akan dilakukan dalam rangka penyelesaian masalah yang akan dibahas sehingga sasaran akhir dari penelitian yaitu hasil perbandingan rangkaian *adder* yang standar pada unit aritmatika dengan rangkaian *adder* yang dikembangkan dengan menggunakan gerbang *NOR* dapat tercapai dan memiliki *output* yang sama serta siap untuk diimplementasikan . Adapun kerangka kerja dari penelitian ini dapat dilihat pada gambar 8 berikut:

Gambar 8 Kerangka Kerja Penelitian

## B. Uraian Kerangka Kerja

Berdasarkan kerangka kerja pada gambar 8 di atas, maka masing-masing langkahnya dapat diuraikan sebagai berikut :

# 1 Pengumpulan Data

Pengumpulan data merupakan hal yang sangat penting dalam sebuah penelitian. Dalam penelitian ini pengumpulan data penulis lakukan melalui :

- a. Jurnal

- Jurnal jurnal yang penulis jadikan sebagai referensi adalah jurnal yang berkaitan dengan sistem rangkaian *adder*, dan yang berhubungan dengan judul yang penulis bahas

- b. Buku yang berhubungan dengan penelitian yang dilakukan Buku yang penulis gunakan sebagai referensi adalah buku yang berkaitan dengan judul yang penulis bahas.

- c. Penelitian Laboratorium (*laboratory research*)

Penelitian laboratorium ini bertujuan untuk melakukan pengujian terhadap penerapan sistem rangkaian adder standar dan rangkaian adder yang dikembangkan dengan menggunakan gerbang NAND dan NOR, khususnya untuk permasalahan perubahan rangkaian *adder* pada unit aritmatika yang ada di dalam ALU. Pada penelitian laboratorium ini tidak terlepas dari piranti atau perangkat yang digunakan, dimana perangkat ini dapat digunakan untuk membantu penulis dalam melakukan pengujian.

Adapun perangkat yang digunakan dalam penyusunan penelitian ini yaitu :

#### a) Perangkat keras

Perangkat ini terdiri dari:

- IC gerbang Logika yang telah disebutkan di bab 2

- LCD 16x2

- Switch tongle

- Dan beberapa perangkat keras pendukung lainnya.

- b) Perangkat lunak

Perangkat ini terdiri dari:

- Sistem Operasi Microsoft Windows 7

- Software AVR C

- Dan beberapa pendukung perangkat lunak lainnya.

#### 2 Identifikasi Masalah

Berikut ini identifikasi masalah dalam sistem rangkaian *adder* yang standar ini adalah :

- 1. Bagaimana rangkaian *adder* yang standar pada unit aritmatika ALU dapat digantikan dengan gerbang lainnya khususnya pada gerbang *NAND* dan NOR?

- 2. Bagaimana hasil dari perbandingan antara rangkaian *adder* standar dengan rangkaian *adder* yang dirubah menggunakan gerbang *NAND* dan NOR?

#### 3 Analisa Sistem

Setelah pengumpulan data dan identifikasi selesai dilaksanakan, maka langkah berikutnya dilakukan adalah analisis terhadap data berupa binary digit rangkaian adder yang standar. Hal ini bertujuan untuk melakukan perbandingan terhadap data rangkaian adder s ır dengan rangkaian adder yang dirubah d 1 gerbang NAND dan NOR tersebut sehingga akan memudahkan penulis di dalam melakukan analisis berikutnya. Sesuai dengan judul penelitian ini yang menggunakan IC gerbang NAND dan NOR sebagai alat untuk membandingkan rangkaian adder standar. Sehingga dengan analisis data ini akan diperoleh gambaran yang jelas terhadap masalah yang dibahas.

# 4 Perancangan Sistem

Pada tahap ini akan membahas tentang perancangan dari model sistem dengan menentukan rancangan input, proses, dan output yang akan digunakan dalam *prototype* rangkaian *adder*. Dalam perancangan sistem ini hal-hal yang akan dilakukan adalah :

# a. Perancangan Model

Model merupakan gambaran dari solusi yang akan dihasilkan, sehingga dari model yang ada, kita dapat mengetahui dan menggambarkan apa yang akan dihasilkan dari proses yang dilakukan nantinya. Dengan demikian penulis membuat suatu model sistem dengan UML (Unified Modelling Language) dalam merancang suatu sistem.

#### b. Penetapan Input

Masukan data *binary digit* untuk perangkat keras pada rangkaian *adder* standar dan rangkaian *adder* menggunakan gerbang *NAND* dan *NOR* adalah sebagai berikut :

- 1. Dalam melakukan perhitungan penjumlahan data 2 (dua) binary digit untuk membandingkan hasil yang didapatkan pada rangkaian adder standar dengan rangkaian adder menggunakan gerbang NAND dan NOR di dalam menentukan hasil penjumlahan binary digit yang diinputkan.

- 2. Menentukan rangkaian apa yang bekerja pada rangkaian *adder* (*half adder* dan *full adder*) tersebut dalam melakukan perhitungan penjumlahan *binary digit*.

- 3. Menentukan jumlah *IC* gerbang logika pada lapisan tersembunyi yang ada di dalam unit aritmatika khususnya rangkaian *adder*.

# c. Penetapan Output

Keluaran sistem yang diharapkan dalam pembuatan *prototype* rangkaian *adder* standar pada unit aritmatika yang ada di dalam ALU dan rangkaian *adder* menggunakan gerbang *NOR* adalah sebagai berikut:

- 1. Dari hasil perhitungan penjumlahan 2 (dua) binary digit manual yang didapat adalah 2 (dua) binary digit yang sama dihasilkan pada prototype rangkaian adder standar maupun rangkaian adder yang dirubah menggunakan gerbang NOR.

- 2. Dari hasil perhitungan penjumlahan pada protoype rangkaian adder yang dibuat akan ditampilkan pada layar LCD 16x2

- 3. Koefisien korelasi pada rangkaian *adder* standar dengan rangkaian *adder* yang dirubah menggunakan gerbang *NOR* dapat ditentukan jika sudah mendapatkan hasil penjumlahan 2 (dua) *binary digit* dari rangkaian *adder* yang dibuat.

- 4. Target (dapat menjadi referensi untuk pengembangan pada rangkaian *adder* yang ada di dalam unit aritmatika pada ALU).

# 5 Implementasi dan Pengujian

## 1. Implementasi Sistem

Tahapan berikutnya yang akan dilakukan dalam penelitian ini adalah melakukan implementasi dari sistem yang telah dirancang. Pada implementasi sistem ini penulis akan membuat sebuah prototype rangkaian elektronik *adder* yang ada pada unit aritmatika di dalam ALU (*Arithmatic Logic Unit*).

#### 2. Pengujian Sistem

Pada tahap ini akan diuji sistem yang telah dibuat tadi. Dengan melihat kemampuan dari sistem

tersebut apakah sudah sama dengan ketentuan yang telah ada dan sesuai dengan yang diharapkan. Kemudian melihat apakah hasil perhitungan penjumlahan 2 (Dua) binary digit yang dihasilkan pada prototype rangkaian adder standar dengan rangkaian adder menggunakan gerbang NAND dan NOR sama atau tidak.

#### IV. ANALISA DAN PERANCANGAN

Analisa sistem yang didapatkan dengan menggunakan metode *deskriptif* adalah perancangan rangkaian gerbang logika yang menggunakan batterai 9 V atau *power supply* sebagai *input* (masukan) tegangan, beberapa IC yang terdiri dari IC 7408,7432,7400,7402,7404 sebagai gerbang logika dasar dengan terhubung pada *push button* untuk logika input 0 (Low) dan 1 (high) dan output keluaran yang dihasilkan adalah dengan lampu LED hidup untuk logika 1 (*High*) dan lampu LED mati untuk logika 0 (*Low*).

Gerbang logika dapat tersusun dari saklar sederhana, *relay*, transistor, dioda, atau IC. Gerbang logika dapat mempunyai beberapa masukan yang masing-masing mempunyai salah satu dari dua keadaan logika, yaitu 0 atau 1. Gerbang logika berdasarkan fungsinya dapat dibedakan menjadi beberapa jenis yaitu gerbang XOR, AND, NAND, dan NOR.

Ada beberapa operasi-operasi dasar pada suatu rangkaian logika dan untuk menunjukkan suatu perilaku dari operasi-operasi tersebut biasanya ditunjukkan dengan menggunakan suatu tabel kebenaran. Tabel kebenaran berisi statemen-statemen yang hanya berisi:

- 1. Benar yang dilambangkan dengan huruf "T" kependekan dari "*True*" atau bisa jugadilambangkan dengan angka 1.

- 2. Salah yang dilambangkan dengan huruf "F" kependekan dari "False" atau bisa juga dilambangkan dengan angka 0.

Gerbang logika adalah piranti dua keadaan, yaitu mempunyai keluaran dua keadaan keluaran dengan nol volyang menyatakan logika 0 (rendah) dan keluaran dengan tegangan tetap yang menyatakan logika 1 (tinggi). Rangkaian digital bipolar sebenarnya adalah rangkaian elektronika digital yang memanfaatkan transistor bipolar sebagai rangkaian gerbang.

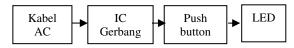

# 4.1 Arsitektur Sistem Rangkaian Gerbang Logika

Gambar 9 Asitektur Sistem Rangkaian Gerbang Logika

#### 4.2 Use Case Diagram

Gambar 10 Use Case Diagram Sistem Half Adder

User mendapatkan indikasi dari perangkat tentang keadaan yang terjadi. Indikasi dibuat dalam 6 (Enam) keadaan. Bila IC gerbang menerima respon tegangan dan respon dari penekanan tombol *push button* maka respon akan ditampilkan pada lampu indikator sesuai dengan kondisi yang direspon oleh IC gerbang.

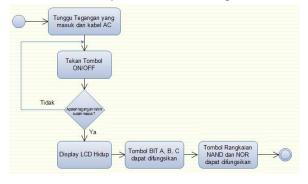

## 4.3 State Machine Diagram

State Machine Diagram merupakan suatu penggambaran behavior sebuah sistem untuk sebuah class tunggal untuk menunjukkan behavior seumur hidup sebuah objek tunggal. Berikut ini gambar 11 State Machine Diagram aliran behavior pada sistem.

Gambar 11 State Machine Diagram Sistem Half Adder

# 4.4 Component Diagram

Component diagram merepresentasikan paket fisik dari modul pengkodean. Component diagram juga menunjukkan interface yang digunakan untuk komunikasi antar komponen. Berikut ini adalah gambar 12 component diagram dari sistem yang dibangun.

Gambar 12 Component Diagram Sistem Half Adder

# 4.6 Perbandingan Rangkaian Half Adder Standar Dengan Inovasi Half Adder

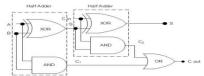

#### 4.6.1 Half Adder Standar

Berikut ini adalah gambar dari Rangkaian Half Adder Standar :

Gambar 4.6 Rangkaian Half Adder Standar

Dari gambar 4.6 didapatkan Hasil Sum dan Carry yang dibuat ke dalam tabel kebenaran, yaitu :

Tabel 4.1 Tabel Kebenaran Half Adder Standar

| INF | PUT | OUT | PUT |

|-----|-----|-----|-----|

| A   | В   | S   | C   |

| 0   | 0   | 0   | 0   |

| 0   | 1   | 1   | 0   |

| 1   | 0   | 1   | 0   |

| 1   | 1   | 0   | 1   |

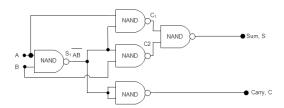

# 4.6.2 Inovasi Half Adder Dengan Gerbang NAND.

Berikut ini adalah gambar rangkaian Inovasi Half Adder dengan gerbang NAND :

Gambar 12 Rangkaian Inovasi Half Adder Dengan Gerbang NAND

Dari gambar rangkaian diatas didapatkan suatu tabel kebenaran yang sama hasil outputnya dengan tabel kebenaran Half Adder Standar.

Tabel 4.2

Tabel Kebenaran Rangkaian Inovasi Half Adder

Dengan Gerbang NAND

| INPUT |   | OUTPUT |   |

|-------|---|--------|---|

| A     | В | S      | C |

| 0     | 0 | 0      | 0 |

| 0     | 1 | 1      | 0 |

| 1     | 0 | 1      | 0 |

| 1     | 1 | 0      | 1 |

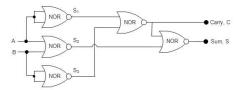

# 4.6.3 Inovasi Half Adder Dengan Gerbang NOR.

Berikut ini adalah gambar rangkaian Inovasi Half Adder dengan gerbang NOR :

Gambar 13 Rangkaian Inovasi Half Adder Dengan Gerbang NOR

Dari gambar rangkaian diatas didapatkan suatu tabel kebenaran yang sama hasil outputnya dengan tabel kebenaran Half Adder Standar.

Tabel 4.3 Tabel Kebenaran Rangkaian Inovasi Half Adder Dengan Gerbang NOR

| INPUT |   | OUTPUT |   |

|-------|---|--------|---|

| A     | В | S      | C |

| 0     | 0 | 0      | 0 |

| 0     | 1 | 1      | 0 |

| 1     | 0 | 1      | 0 |

| 1     | 1 | 0      | 1 |

# V. IMPLEMENTASI DAN PEMBAHASAN

## 5.1 Tahapan Implementasi

Berikut ini tahapan implementasi sistem yang terdiri dari langkah-langkah sebagai berikut :

# 1. Menerapkan Rencana Implementasi

Dalam rencana implementasi ini, dimaksudkan untuk mangatur biaya dan waktu yang dibutuhkan selama implementasi sistem berjalan. Semua biaya yang akan dikeluarkan untuk kegiatan implementasi sistem ini perlu dianggarkan dalam bentuk anggaran biaya. Karena anggaran biaya ini, berfungsi sebagai pengendalian terhadap biaya-biaya yang harus dikeluarkan. Waktu yang dibutuhkan untuk melakukan kegiatan juga diperlukan dalam rencana implementasi dalam bentuk schedul

waktu. *Schedul* waktu juga berfungsi sebagai pengendalian terhadap waktu implementasi.

- 2. Menjalankan Kegiatan Implementasi

- a. Pemilihan dan pelatihan personil

- b. Pemilihan tempat dan instalasi perangkat keras dan perangkat lunak

- c. Pemrograman perangkat lunak dan Perancangan perangkat keras

- d. Pengujian sistem.

# 3. Tindak Lanjut Implementasi

Dalam hal ini setelah implementasi adalah pengujian. Pengujian disini dilakukan dengan cara mengujicoba perangkat yang telah selesai dirancang. Apakah telah sesuai dengan implementasi yang telah direncanakan sebelumnya.

# 5.2 Tujuan Implementasi

Tujuan implementasi adalah untuk mengetahui bagaimana sistem yang telah dirancang dapat berjalan sesuai dengan hasil rancangan. Dalam hal ini penulis merancang sebuah perangkat keras gerbang logika (OR, AND, NOT, NOR, dan NAND). Perangkat ini dirancang untuk memodelkan keadaan pemberian logika biner nol (0) atau satu (1) ke dalam IC gerbang logika. Agar mengetahui bagaimana sistem digital sebenarnya di dalam menghasilkan bilangan biner nol (0) atau satu (1) yang sering dijumpai pada sirkuit digital yang diimplementasikan secara elektronik.

# 5.3 Implementasi dan Pembahasan

Dari perancangan alat gerbang logika dasar yang telah dilakukan pada penelitian ini didapat hasil :

# 1. Perancangan Gerbang logika Awal

Gambar 14 Perancangan Awal Gerbang Logika dan Peletakkan Komponen

Perancangan awal gerbang logika dasar dengan meletakkan beberapa komponen diantaranya adalah IC gerbang, *push button* dan LED pada PCB dengan bantuan solder dan timah seperti yang ditujukkan pada gambar 14 diatas.

#### 2. Hasil Perakitan dengan *Output* LED

Prototype kemudian diuji coba dengan menekan push button untuk 2 input pada masing-masing gerbang diantaranya adalah gerbang AND, OR, NOT, NAND dan NOR seperti pada gambar 15.

Gambar 15 Hasil Perakitan Dengan Output LED

3. Hasil Perakitan Dengan Logika Inputan *Push Button*

Pada hasil perakitan ini dilakukan pengujian yang ditunjukkan pada gambar 5.5 dengan peng-inputan logika biner satu (1), dengan menekan tombol *push button* pada masing-masing IC gerbang logika yang outputnya adalah lampu indikator LED hidup yang dapat dilihat langsung pada rangkaian gerbang logika.

Gambar 16 Hasil Perakitan Dengan Logika Inputan Push Button

#### VI. KESIMPULAN DAN SARAN

## 6.1 Kesimpulan

Adapun kesimpulan dari kegiatan penelitian ini pada program PDP, yaitu :

- 1. *Prototype* yang dihasilkan dari kegiatan PDP ini dapat dipergunakan sebagai alat simulasi pembelajaran sistem digital dalam memahami rangkaian *adder* dalam menjalankan perhitungan penjumlahan.

- 2. *Prototype* yang dihasilkan dapat memberikan perbandingan yang sama dari rangkaian *adder* standar dan rangkaian inovasi *adder*.

- 3. *Prototype* yang dibuat ini dapat memberikan pengetahuan kepada mahasiswa bahwa rangkaian *adder* standar tersebut dapat digantikan dengan rangkaian *adder* yang menggunakan gerbang NOR dan NAND.

# 6.2 Saran

Adapun saran dari kegiatan penelitian ini pada program PDP, yaitu :

Prototype yang dibuat masih jauh dari kesempurnaan, yakni rangkaian prototype yang dihasilkan tidak dapat memperlihatkan output dari penjumlahan rangkaian adder standar dan rangkaian inovasi adder

- kedepannya dapat dikembangkan sehingga dapat menghasilkan *output* seperti yang telah disebutkan.

- Prototype yang dibuat belum lengkap dalam memahami sistem perhitungan yang dilakukan oleh gerbang logika, seperti penjumlahan, pengurangan, perkalian, dan pembagian. Kedepannya masih dapat dikembangkan lagi seperti yang telah disebutkan diatas.

- 3. *Prototype* yang dibuat masih belum dapat menjumlahkan bilangan 8 bit. Kedepannya masih dapat dikembangkan lagi, sehingga dapat menjumlahkan bilangan 8 bit.

#### 7. DAFTAR PUSTAKA

- [1] Mathius Nugroho. 2015. Rangkaian Adder Dengan Seven Segment. Skripsi. Fakultas Teknologi Industri Universitas Internasional, Batam

- [2] Kurniawan, Fredly.2005. *Jurnal Sistem Digital Konsep Dam Aplikasi Volume 3*. Yogyakarta: Gava Media

- [3] Abdul Jabar. (2011). "Pemodelan dan Simulasi Dinamis Pendeteksi Dini Gempa Pada Gedung ". Universitas Putra Indonesia YPTK Padang: Tesis M.Kom.

- [4] Law, A. and Kelton W., 2000, "Simulation Modelling and Analysis", 3<sup>rd</sup>, Mc Graw-Hill.

- [5] Martin Fowler. (2005). "UML Distilled." 3th. Ed. A Brief Guide to the Standard Object Modelling Language: Andi. 151-160.