# A Design Approach of Multipliers in FIR Filter using VHDL

# Nitin Vashistha, Sunil Sharma

*Abstract*— A multiplier is one of the key equipment obstructs in most digital and high frameworks, for example, FIR filter, digital signal processors and microprocessors and so forth. This venture introduces a proficient execution of rapid multiplier utilizing the shift and add technique, Radix\_2, Radix\_4 modified Booth multiplier algorithm. In this task we look at the working of the three multipliers by actualizing each of them independently in FIR filter. The parallel multipliers like radix 2 and radix 4 modified booth multiplier does the calculations utilizing lesser adders and lesser iterative advances. Because of which they involve lesser space when contrasted with the serial multiplier. This is an imperative basis in light of the fact that in the manufacture of chips and elite framework requires segments which are as little as could reasonably be expected.

In our undertaking when we look at the power utilization of the considerable number of multipliers we locate that serial multipliers devour more power. So where control is a critical paradigm there we ought to incline toward parallel multipliers like booth multipliers to serial multipliers. The low power utilization nature of corner multiplier settles on it a favored decision in planning distinctive circuits

In this venture we initially composed three distinctive sort of multipliers utilizing shift and add technique, radix 2 and radix 4 modified

booth multiplier algorithm. We utilized diverse sort of adders like sixteen bit full adder in outlining that multiplier. At that point we planned a 4 tap delay FIR filter and set up of the augmentation and increases we executed the segments of various multipliers and adders. At that point we looked at the working of various multipliers by contrasting the power utilization by each of them. The consequence of our undertaking causes us to pick a superior choice amongst serial and parallel multiplier in manufacturing diverse frameworks. Multipliers shape a standout amongst the most essential parts of numerous frameworks. So by examining the working of various multipliers outlines a superior framework with less power utilization and lesser zone. The consequence of our undertaking encourages us to settle on a legitimate decision of various multipliers in creating in various number juggling units and settling on a decision among various adders in various advanced applications as per prerequisites

*Index Terms*— Finite Impulse Response, radix\_2 and radix\_4 Booth multiplier, Shift and add multiplier.

## I. INTRODUCTION

The parallel multipliers like radix 2 and radix 4 modified booth multiplier does the calculations utilizing lesser adders and less

Iterative strides. Because of which they involve lesser space when contrasted with the serial multiplier. This is an essential standard in light of the fact that in the creation of chips and

Nitin Vashistha, M.Tech Scholar, Pacific University, Udaipur

high performance framework requires segments which are as little as could reasonably be expected.

In this paper when we compare at the power consumption of the considerable number of multipliers we locate that serial multipliers devour more power. So where power is a critical paradigm there we ought to favor parallel multipliers like booth multipliers to serial multipliers. The low power utilization nature of booth multiplier settles on it a favored decision in planning diverse circuits.

At that point we outlined a 4 tap delay FIR filter and set up of the multiplication and additions we actualized the parts of various multipliers and adders. At that point we analyzed the working of various multipliers by comparing at the power consumption by each of them. The after effect of our task causes us to pick a superior alternative amongst serial and parallel multiplier in creating diverse frameworks. Multipliers frame a standout amongst the most critical segment of numerous frameworks.

## II. ARCHITECTURE OF A RADIX 2^N MULTIPLIER

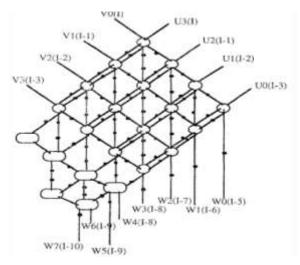

The architecture of a radix 2<sup>n</sup> multiplier is given in the Figure. This square graph demonstrates the multiplication of two numbers with four digits each. These numbers are meant as V and U while the digit estimate was picked as four bits. The purpose behind this will end up plainly clear in the accompanying segments. Each circle in the figure relates to a radix cell which is the core of the outline. Each radix cell has four digit inputs and two digit outputs.

Fig. 1 Architecture of a radix 2

#### III. BOOTH MULTIPLICATION ALGORITHM

Booth algorithm gives a procedure for multiplying binary integers in signed –2's complement representation.

Sunil Sharma, Assistant Professor, Department of ECE, Pacific University, Udaipur

| U    | V    | X    | X-1 |                       |

|------|------|------|-----|-----------------------|

| 0000 | 0000 | 1100 | 0   | Load the valu         |

|      |      | [    |     | 1" cycle              |

|      |      |      |     | 2 <sup>nd</sup> cycle |

|      |      |      |     | A CVCIE               |

|      |      |      |     | 4th Cycle             |

## Table 1. Booth Algo

#### IV. RADIX-4 FFT ALGORITHM

When the number of data points N in the DFT is a power of 4 (i.e.,  $N = 4^{v}$ ), we can, of course, always use a radix-2 algorithm for the computation. However, for this case, it is more efficient computationally to employ a radix-r FFT algorithm.

Let us begin by describing a radix-4 decimation-in-time FFT algorithm briefly.

## V. RESULTS OF DIFFERENT MULTIPLIERS

| Number of Slices           | 81    |

|----------------------------|-------|

| Number of 4 input LUTs     | 140   |

| Number of bonded INPUT     | 16    |

| Number of bonded<br>OUTPUT | 16    |

| CLB Logic Power            | 2.40W |

#### Table.2 Array Multiplier

| Number of Slices       | 77     |

|------------------------|--------|

| Number of 4 input LUTs | 141    |

| Number of bonded INPUT | 16     |

| Number of bonded       | 16     |

| OUTPUT                 |        |

| CLB Logic Power        | 2.023W |

|     | Table. | 3Booth | Mu | ltiplier | •  |

|-----|--------|--------|----|----------|----|

| 011 |        |        |    |          | 07 |

| Number of              | Slices |        | 97    |

|------------------------|--------|--------|-------|

| Number of 4 input LUTs |        |        | 171   |

| Number of bonded INPUT |        |        | 16    |

| Number                 | of     | bonded | 17    |

| OUTPUT                 |        |        |       |

| CLB Logic Power        |        |        | 1.84W |

|                        |        |        |       |

Table. 4 Radix -4 Booth Multiplier

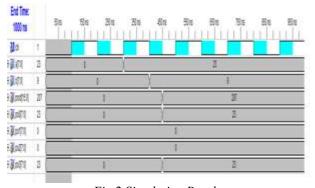

Fig.2 Simulation Results

#### VI. CONCLUSION

While looking at the radix 2 and the radix 4 booth multipliers we found that radix 4 devours lesser power than that of radix 2. This is on account of it utilizes half number of emphasis and adders when contrasted with radix 2. At the point when all the three multipliers were thought about we found that array multipliers are most power

consuming and have the greatest area. This is on the grounds that it utilizes an extensive number of adders. Accordingly it backs off the framework since now the framework needs to do a considerable measure of computation. Multipliers are one the most essential part of numerous frameworks. So we generally need to locate a superior arrangement if there should arise an occurrence of multipliers. Our multipliers ought to dependably devour less power and cover less power. So through our undertaking we endeavor to figure out which of the three calculations works the best. At last we establish that radix 4 adjusted stall calculations works the best.

#### REFERENCES

- L. R. Rabiner, B. Gold, "Theory and Application of Digital Signal Processing," Englewood Cliffs, NJ: Prentice-Hall, 1975.

- [2] Shen-Fu Hsiao, Member, IEEE, and Wei-Ren Shiue," Design of Low-Cost and High-Throughput Linear Arrays for DFT Computations: Algorithms, Architectures, and Implementations", Ieee Transactions On Circuits And Systems—Ii: Analog And Digital Signal Processing", VOL. 47, NO. 11, NOVEMBER 2000

- [3] Jung-yeol Oh, Myoung-seoh Lim" Fast Fourier Transform Processor Based on Low-power and Area-efficient Algorithm" 2004 IEEE Asia-Pacific Conference on Advanced System Integrated Circuits(AP-ASIC2004)/ Aug. 4-5,2004

- [4]Ramya Muralidharan, Chip-Hong Chang, "Radix-8 Booth Encoded Modulo Multipliers With Adaptive Delay for High Dynamic Range Residue Number System" IEEE transactions on circuits and systems—i: regular papers, vol. 58, no. 5, may 2011

- [5]K. Likharev and V. Semenov, "RSFQ logichemory family: a new Josephson-junction technology for sub-terahertz-clock-frequency digital systems," IEEE Trans. Appl. Superconductivity, vol. 1, pp. 3-28, March 1992.

- [6] A. Mukhanov, "Superconductive single-flux-quantum technology". in: ISSCC Digest of Technical Papers, San Francisco, CA, USA, pp. 126-127,321, F

- [7] L. Adlemsn, R. L. Rivest, and A. Shamir, "A method for obtaining digital signat.ure and public-key cryptosystems," Comm. of the ACM, vel. 21, no. 2, pp. 120-126, February 1978.

- [8] M. E. Heilman and W. Diffie, "New directions on cryptography," IEEE transactions on Infonation Theory, wi. 22, pp. 644-654, November 1976.

- [9] L. A. Tawaibeh, "Radix-4 ASIC Design of B Scalable Montgomery Modular Muhipiier using Encoding Techniques," M.S. thesis, Oregon %ate University, USA, October 2002

- [10] Alexandre F. Tenca, Lo'ai A. Tawalbeh Department of Electrical & Computer Engineering" An Efficient and Scalable Radix-4 Modular Multiplier Design Using Recoding Techniques" Oregon State University, Corvallis, Oregon 97331, USA

- [11]John paul shen and f. joel ferguson"The Design of Easily Testable VLSI Array Multipliers" IEEE transactions on computers, vol. c-33, NO. 6, JUNE 1984

- [12] T. Sridhar and J. P. Hayes, "A functional approach to testing bit-sliced microprocessors," IEEE Trans. Comput., vol. C-30, pp. 563-572, Aug. 1981.

- [13] C. Mead and L. Conway, Introduction to VLSI Systems. Reading, MA: Addison-Wesley, 1980.

- [14]Denyer, P.B., and Renshaw, D.: 'VLSI signal processor a bit-serial approach' (Addison-Wesley, 1985)

- [15] Kung, S.Y.: 'VLSI array processors' (Prentice-Hall, Englewood Cliffs, NJ, 1988)

- [16]Smith, S.G., McGregor, M.S., and Denyer, P.B.: 'Techniques to increase the computational throughput of bit-serial architectures'. IEEE Int.

Conf. on Acoustics, Speech, and Signal Processing, ICASSP, Dallas, TX, USA, 1987, pp. 543–546

- [17] A. Liakot, S. Roslina, A. Ishak, and M.A. Alauddin, "Design of a Micro-UART for SoC Application," Computer and Electrical Engineering, Elsevier, Vol. 30, Issue 4, pp. 257-268, June 2004.

- [18] L. Petroli, C.A. Lisboa, F.L. Kastensmidt, and L. Carro, "Using Majority Logic to Cope with Long Duration Transient Faults," Proc. of the 20th annual conference on Integrated circuits and systemsdesign, pp. 354-359, 2007.

- [19]K.H. Tsoi, P.H.W. Leong, "Mullet a parallel multiplier generator," fpl, pp.691-694, International Conference on Field Programmable Logic and Applications, 2005, 2005

- [20] S. Tahmasbi Oskuii, P. G. Kjeldsberg, and O. Gustafsson, "Transition activity aware design of reduction-stages for parallel multipliers," in Proc. 17th Great Lakes Symp. On VLSI, March 2007, pp. 120–125.

- [21] Ayman A. Fayed, Magdy A. Bayoumi, "A Novel Architecture for Low-Power Design of Parallel Multipliers," vlsi, pp.0149, IEEE Computer Society Workshop on VLSI 2001, 2001

- Books referred:

- [22]. Pedroni Circuit, "Design using VHDL", Massachussets Institute of Technolgy, 2004.

- [23] VHDL by Sjoholm Stefan

- [24] VHDL by J. Bhaskar

- [25] Johny R Johnson, "Digital Signal Processing", PHI publications.

- [26] Vallavraj & Salivhanan, " Digital Signal Processing", TMH publications.

- [27] Christos Meletis, Paul Bougas, George Economakos, Paraskevas Kalivas and Kiamal Pekmestzi, "High-Speed Pipeline Implementation of Radix-2 DIF Algorithm", World Academy of Science, Engineering and Technology 2 2005