#### [Vol-4, Issue-3, Mar- 2017] ISSN: 2349-6495(P) / 2456-1908(O)

## Implementation of CMOS Low Dropout Voltage Regulator with Frequency divider for Improved Stability

Kamlesh Sharma<sup>1</sup>, Gajendra Sujediya<sup>2</sup>, Abdul Naim Khan<sup>3\*</sup>

<sup>1,2</sup>Department of ECE, Rajasthan Institute of Engineering & Technology, Jaipur, India <sup>3</sup>Department of ECE, Jaipur National University, Jaipur, India

Abstract— A Amplifier is a gadget that is use to intensify the flag quality. The outline of superior and stable low drop-out voltage controllers is a test these days with diminishing gadget sizes and expanding power densities. The proposed circuit is recreated utilizing Cadence ORCAD Capture in 180nm CMOS innovation parameters with the supply voltage of 1.8V. It works at low request supply voltages and gives adequate yield stack current even with negligible utilization of info current. Proposed LDO engineering enhanced the transient reaction. The proposed configuration enhances soundness and gives superior as far as PSRR and slew rate, which are critical performing parameters for a LDO.

Keywords-MOS, LOWDROPOUT, MOSFET, ORCAD, PSRR.

#### I. INTRODUCTION

Compact Devices Such as mobile, Laptop, Calculator, etc. have become so popular and so has become the need of keeping them charged for longer times. Controllers have become an important part of power management system with the growing demand of portable battery operated products. LDO's work at low power inputs and low load current. Low power consumption makes them ideal for use in portable low energy requirement circuits. A Device cannot perform without energy and needs a stable and powerful supply voltage.

Complementary Metal Oxide Semiconductor (CMOS) is the semiconductor innovation utilized as a part of the transistors that are fabricated into the majority of today's PC microchips. Semiconductors are made of silicon and germanium, materials which "somehow" lead power, yet very little more. [1] LDOs (Low dropout controllers) are a straightforward reasonable approach to direct a yield voltage that will be fueled from a higher voltage input. They are anything but difficult to outline with and utilize. For a large portion of the applications, the parameters in a LDO (Low dropout controllers) datasheet are generally straightforward. In spite of the fact that, alternate applications require the architect to concentrate the

datasheet all the more nearly to check regardless of whether the LDO is appropriate for the particular circuit conditions. [2]

#### II. LOW DROPUT VOLTAGE REGULATOR

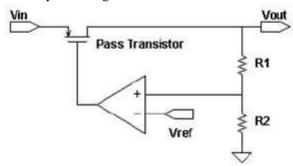

A low dropout or LDO controller is a DC straight voltage controller which has an exceptionally minor data yield differential voltage. The principle modules are a force FET and a differential intensifier (blunder speaker). One info of the differential intensifier shows a rate of the yield, as firm by the resistor proportion of R1 and R2. The second data to the differential enhancer is from a steady voltage reference (band hole reference). If the yield voltage increases too high close to the reference voltage, the drive to the power FET changes to keep a reliable yield voltage.

Fig. 2.1: LDO Voltage Regulators

#### 2.1 Feedback Network:

The information framework makes the yield voltage to be differentiated and the voltage reference. This voltage is made by a voltage divider is given as:

$$V_{out} = V_{ref} \left( 1 + \frac{R_1}{R_2} \right) \quad ..... (2.1)$$

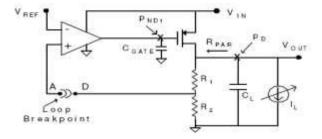

#### 2.2 General Architecture of LDO:

As a given particular estimation of CL is 1uF and for great burden current (200mA) size of pass transistor is substantial so aftereffect of which door capacitor of pass transistor is likewise huge in the scope of couple of hundred of pF [28]. This estimation of entryway capacitor

<u>www.ijaers.com</u> Page | 156

[Vol-4, Issue-3, Mar- 2017] ISSN: 2349-6495(P) | 2456-1908(O)

of pass transistor is vast contrast with the yield capacitor of blunder intensifier.

$$\left[\frac{W}{L}\right]_{PASS} = 2 \frac{I_{MAX}}{\mu C_{ox} V_{DSsat}^2} \dots (2.2)$$

Fig.2.2: Typical LDO Open Loop Representations

Because of these gauges of capacitors the average LDO open circle reaction can be approximated by a second request exchange capacity given as:

$$H(S) = \frac{A_O}{\left(1 + \frac{S}{P_D}\right)\left(1 + \frac{S}{P_{ND1}}\right)} \dots (2.3)$$

This exchange capacity has two posts that are straight identified with the shafts marked in Fig. 3.2 and can be start at the yield of framework  $(P_D)$  and at the entryway of pass transistor  $(P_{ND1})$ .

$$P_D \approx \frac{1}{2\pi R_{PAR}C_L} \dots (2.4)$$

$$P_{ND1} \approx \frac{1}{2\pi R_A \left(C_{GATE} + R_{PAR}g_{mp}C_{GD} + C_{GD}\right)} \dots (2.5)$$

These shafts take after the deviations the pass component encounters when a change in burden current is experienced on the grounds that the yield resistance of the LDO ( $R_{PAR}$ ) is given by:

$$R_{PDR} = r_{DS} || R_1 + R_2 || R_L \dots (2.6)$$

The yield impedance ( $R_{PAR}$ ) screens varieties in burden in light of the fact that both  $R_L$  and  $r_{DS}$  are elements of the heap current. The channel to-source impedance  $r_{DS}$  of the PMOS pass component has a reliance on burden current that is given by (2.7)

$$r_{DS} = \frac{1}{\lambda I_{DS}} \dots (2.7)$$

#### 2.3 Output Noise:

The yield commotion voltage is generally educated as the RMS yield clamor voltage over a predetermined recurrence band (10Hz to 100 kHz) under the circumstances of a characterized yield voltage, a swell free information voltage and consistent burden current.

#### 2.4 Load Regulation:

Load regulation is the capacity of the controller to keep up the fancied yield voltage with any adjustments in burden current. Load regulation can be measured by changing the heap current and measuring the adjustments in yield voltage.

Load Regulation

$$\Xi \frac{\Delta V_0}{\Delta I_0}$$

.....(2.8)

#### 2.5 Line Regulation:

Line regulation is the capacity of the circuit to support the predefined yield voltage with no impacts from deviations in info voltage. Line regulation can be measured by giving the supply voltage a short heartbeat and demonstrating the power of the circuit to this heartbeat. Line regulation can likewise be communicated as:

Line Regulation

$$\equiv \frac{\Delta V_o}{\Delta V_I}$$

.....(2..9)

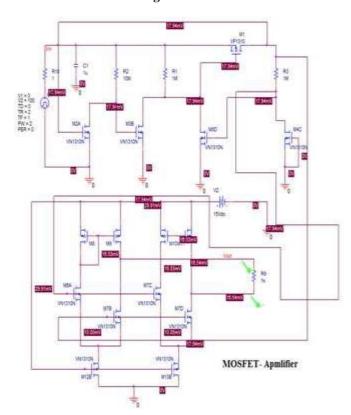

# III. LDO EXPERIMENTAL CIRCUIT'S 3.1 LDO with Frequency driver and without current steering circuit:

Fig. 3.1: Reference LDO with Frequency driver and without current steering circuit

#### 3.1.1 Circuit Implementation:

Failure voltage is the input to output voltage difference at which the LDO is no longer able to regulate against further decreases in the input voltage. In the dropout region, the pass element acts like a resistor with a value equal to the drain to source on resistance. The competence of an LDO is determined by the ground current and input output voltages. Load regulation is the amount of the LDO's ability to sustain the definite output voltage under changing capacity situations. The line transient response is the output voltage difference for an

[Vol-4, Issue-3, Mar- 2017] ISSN: 2349-6495(P) / 2456-1908(O)

input voltage stage change.it is a function of the gain bandwidth of the LDO's control loop, and the size and slew rate of the input voltage change. PSRR is not defined by a single value because it is frequency dependent. An LDO consists of a reference voltage, error amplifier, and a power-pass element, such as mosfet or bipolar transistor. The error amplifier provides dc gain to regulate the output voltage. The ac gain of the error amplifier in large part determines the PSRR. A typical LDO can have as such as 80dB of PSRR at 10 Hz, but the PSRR can fall to as little as 20dB a few tens of kilohertz.

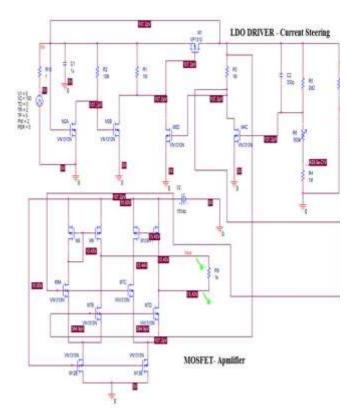

#### 3.2 LDO with current steering without amplifier:

Fig.3.2: Reference LDO with current steering without amplifier

#### 3.2.1 Circuit Implementation:

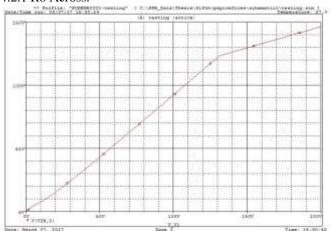

In this implementation we have designed a Ldo with current steering without amplifier. Input pulse is varying from 0v to 100v and its give a stable output at higher range. And also gives a gain of high order and we also calculate the output voltage at multiport but there is disadvantage that its gives the low output voltage order of mv. And also gives high dropout voltage. Values of output voltage, gain and Transient time is calculated at multiport as changing the position of voltage probe.

Low-dropout regulators (LDOs) are deceptively simple devices that provide critical functions such as isolating a load from a dirty source or creating a low-noise source to power sensitive circuitry. In this work we have presented a LDO Circuit, Low Drop-Out Voltage Regulator which is intended to work over a wide range of input voltage, typically the system has been tested over the 10V and the system responded well with a constant output of 1.57V, with few minute spikes after the input voltage ranges crosses the 750V mark and makes the output reach to the 1.61V.

Voltage regulators are useful for the digital circuits as the digital components are intended and designed in such a way that they consumes less input power and are able to work at very low power voltages, as it is the necessity of the modern day gadgets as well.

The Circuit designed here comprises of several sections which are responsible for achieving the constant low dropped out voltage. The designed circuit comprises of the Startup Circuit, Current Steering Circuit, Current Frequency Driver, CMOS Inverter Circuit, CMOS Amplifier Circuit and MOSFET Driver Circuit. All the modules developed in this work are the combination of several n and p MOSFETs.

#### III. SIMULATIONS AND RESULTS

This chapter will discuss the result of the implemented project and tools & technology which is used.

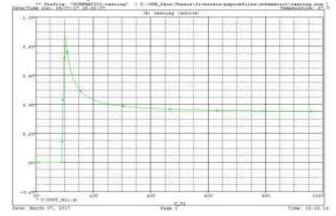

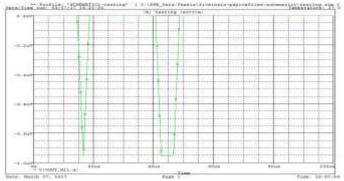

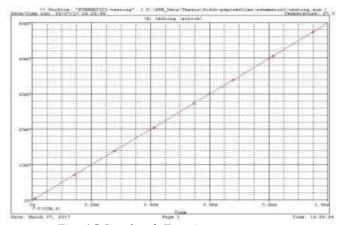

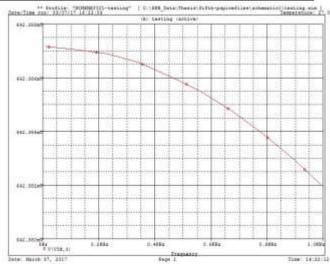

4.1 Results of LDO with Frequency driver and without current steering circuit:

Fig: 4.1 Simulated\_Output\_Voltage

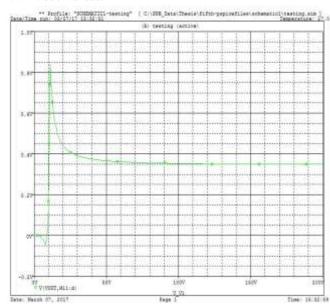

Fig: 4.2 Simulated\_Transient\_response

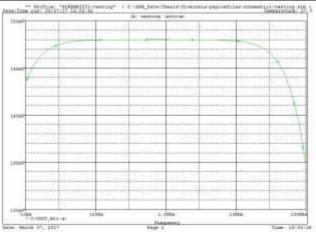

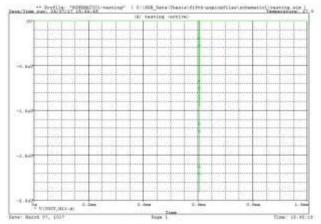

Fig: 4.3 Simulated\_gain

### 4.2 Results of LDO with current steering without amplifier:

#### 4.2.1 R8 Across:

Fig: 4.4 Simulated\_Output\_Voltage

Fig: 4.5 Simulated\_Transient\_response

Fig: 4.6 Simulated\_gain

#### 4.2.2 Vout Across:

Fig: 4.7 Simulated\_Output\_Voltage

Fig: 4.8 Simulated\_Transient\_response

Fig: 4.9 Simulated\_gain

#### 4.2.3 Both Across (R8 and Vout):

Fig: 4.10 Simulated\_Output\_Voltage

Fig: 4.11 Simulated\_Transient\_response

Fig: 4.12 simulated\_gain

Table.4.1: Comparison of proposed circuit with the LDOs available in literature

| available in literature |       |       |     |      |      |      |

|-------------------------|-------|-------|-----|------|------|------|

| Parame                  | Desig | Desig | Bas | Pape | Pape | Pape |

| ters                    | n 1   | n 2   | e   | r1   | r2   | r3   |

|                         |       |       | Pap |      |      |      |

|                         |       |       | er  |      |      |      |

| Vin                     | 10 –  | 10 –  | 3V- | 2.0V | N/A  | N/A  |

|                         | 500V  | 500V  | 5.5 |      |      |      |

|                         |       |       | V   |      |      |      |

| Vout                    | ~1.6  | ~1.6  | ~1. | ~1.8 | ~1.8 | 0.9V |

|                         | V     | V     | 8   |      |      |      |

| Iout(Ma                 | 0.97  | 1.27  | 1.2 | N.A. | N.A  | 100  |

| x)                      | mA    | mA    | 5m  |      |      | mA   |

|                         |       |       | Α   |      |      |      |

| I <sub>out</sub> (Mi    | -     | -     | N   | N.A  | N.A. | 6m   |

| n)                      | 0.47  | 1.14  | M   |      |      | A    |

|                         | mA    | mA    |     |      |      |      |

| Line                    | 18.29 | 17.24 | 2.7 | N.A. | 2m   | N.A. |

| Regulat                 | mV    | mV    | mV  |      | V    |      |

| ion                     |       |       |     |      |      |      |

| Voltag                  |       |       |     |      |      |      |

| e                       |       |       |     |      |      |      |

| Load                    | 17.49 | 18.34 | 0.3 | N.A. | 34m  | N.A. |

| Voltag                  | mV    | mV    | mV  |      | V    |      |

| e                       |       |       |     |      |      |      |

| PSRR                    | 54db  | 57db  | 44d | N.A. | >45  | N.A. |

|                         | @10   | @10   | B@  |      | dB   |      |

|                         | kHz   | kHz   | 10k |      |      |      |

|                         |       |       | Hz  |      |      |      |

| Dropou                  | 8.27  | 8.09  | 1.2 | N.A. | N.A. | N.A. |

| t                       | V     | V     | V   |      |      |      |

| voltage                 |       |       |     |      |      |      |

| Settling                | 12ns  | 12ns  | 2us | <5us | N.A. | 5.45 |

| Time                    |       |       |     |      |      | 5ns  |

| Delta                   | 81m   | 78m   | 56  | <70  | 54m  | 90M  |

| vout                    | V     | V     | mV  | mV   | V    | v    |

#### IV. CONCLUSION

Low Drop Out voltage regulators are the regulators which can generate the output form the very low voltage or from the input voltage equivalent to the range of the output voltage, however the ideal cases are not applicable to the practical solutions. In this work we have suggested a LDO circuit which comprises of various circuits like current steering, CMOS inverter, CMOS amplifier, current frequency driver and circuits like startup circuit. this LDO design will prove to be of great utility. Furthermore, the circuit can deliver higher addition than the reference circuit. The configuration additionally succeeds low space as the resistors and capacitor are kept away from.

#### REFERENCES

- [1] Amit P. Patel and Gabriel A. Rincón-Mora, "High Power-Supply-Rejection (PSR) Current-Mode Low-Dropout (LDO) Regulator," IEEE Transactions on Circuits and Systems—II: Express Briefs, Vol. 57, No. 11, November 2010.

- [2] Hung-Chih Lin, Hsiang-Han Wu, and Tsin-Yuan Chang, "An Active-Frequency Compensation Scheme for CMOS Low-Dropout Regulators with Transient-Response Improvement," IEEE Transactions on Circuits and Systems—II: Express Briefs, VOL. 55, NO. 9, September 2008.

- [3] Socheat Heng and Cong-Kha Pham, "A Low-Power High-PSRR Low-Dropout Regulator with Bulk-Gate Controlled Circuit," IEEE Transactions on Circuits and Systems—II: Express Briefs, Vol. 57, No. 4, April 2010.

- [4] Liake Wang, Jinguang Jiang, Shanshan Li, Xu Gong and Qingy un Li, "A High Stability Low Drop-out Regulator With Fast Transient Response," IEEE 978-1-4244-5849-3/10/\$26.00 ©2010.

- [5] Robert J. Milliken, Jose Silva-Martínez, and Edgar Sánchez-Sinencio, "Full On-Chip CMOS Low-Dropout Voltage Regulator," IEEE Transactions on Circuits and Systems—I: Regular Papers, Vol. 54, No. 9, September 2007.

- [6] SreehariRao Patri, and K. S. R. KrishnaPrasad, "Self Compensating ON Chip LDO Voltage Regulator in 180nm," World Academy of Science, Engineering and Technology 44 2008.

- [7] Peter Hazucha, Tanay Karnik, Bradley A. Bloechel, Colleen Parsons, David Finan, and Shekhar Borkar, "Area-Efficient Linear Regulator With Ultra-Fast Load Regulation," IEEE Journal of Solid-State Circuits, Vol. 40, No. 4, April 2005.

- [8] David C. W. Ng, David K. K. Kwong, and Ngai Wong, "A Sub-1 V, 26 W, Low-Output-Impedance CMOS Bandgap Reference With a Low Dropout or

- Source Follower Mode," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 19, No. 7, July 2011.

- [9] Chenchang Zhan, and Wing-Hung Ki, "Output-Capacitor-Free Adaptively Biased Low-Dropout Regulator for System-on-Chips," IEEE Transactions on Circuits and Systems—I: Regular Papers, Vol. 57, No. 5, May 2010.

- [10] Abdul Naim Khan and Sandeep Kumar Toshniwal, "Multi-level CMOS LDO-Voltage Circuit with Differential Current Circuit Steering and Regulated Voltage," IOSR Journal of VLSI and Signal Processing, Volume 5, Issue 5, Ver. I, PP 40-46, Oct 2015.

- [11] Edward N. Y. Ho and Philip K. T. Mok, "A Capacitor-Less CMOS Active Feedback Low-Dropout Regulator with Slew-Rate Enhancement for Portable On-Chip Application," IEEE Transactions on Circuits and Systems—II: Express Briefs, Vol. 57, No. 2, February 2010.