# Ultra High MULTI CLOCK FREQUENCY BAUD RATE 128 Bit Multichannel PRBS CODEC ASIC I.P Core Design for High speed wireless internet Wi-Fi Routers, MODEM's, NIC's

Prof P.N.V.M Sastry<sup>1,</sup> Prof.Dr.D.N.Rao<sup>2</sup>, Dr.S.Vathsal<sup>3</sup>

<sup>1</sup>Dean-IT EDA Software MNC CELL & R&D CELL &ECE, J.B.R.E.C, Yenkapally, Moinabad, Hyderabad, India <sup>2</sup>Dean R&D, J.B.I.E.T, Yenkapally, Moinabad,, Hyderabad, India <sup>3</sup>Professor R&D, AERO Dept., I.A.R.E, Hyderabad, India

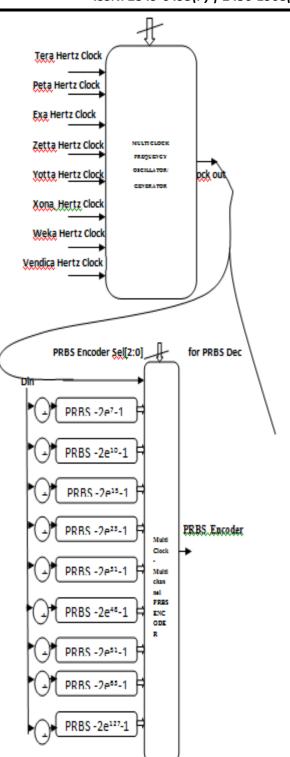

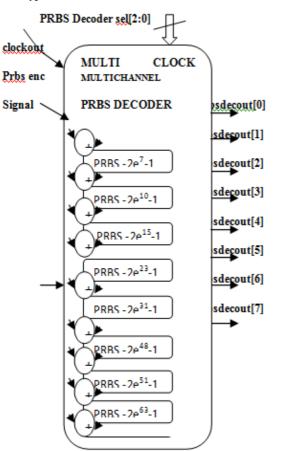

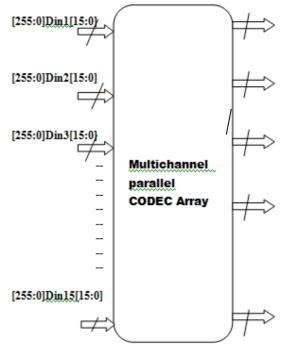

Abstract— The main aim is for HDL Design and Implementation of 128 Bit Multichannel PRBS CODEC for High Speed wireless internet computing products like Wi-Fi Routers, MODEM's. this is very suit for very high speed internet computing products / applications of Big Parallel Network Data MODEM Interface based Computing Servers/Stations. This design consists of PRBS Encoder and Decoder Design of Different Channel in terms of different PRBS Patterns Frequencies Sequences  $-2e^{7}-1,2e^{10}-1, 2e^{15}-1, 2e^{23}-1, 2e^{31}-1, 2e^{48}-1,$  $2e^{52}$ ,  $2e^{64}$ ,  $1, 2e^{128}$ -1 by tapping through different feedback elements. Tapping of PRBS Done as per C.C.I.T.T - I.T.U 0.150, 0.151, 0.152, 0.153 Standards. these pattern sequences are encoded and decoded through different PRBS channel type selector/de-selector and outputs are generated through serial and parallel form of different PRBS Patterns. Programming design description done by Verilog HDL/VHDL and Design Synthesis & Implementation done through Xilinx ISE Software and Debugging done by Advanced FPGA Development Boards/Kits. Design Verification done through highly proficient Test Bench/Stimulus Design Module Codes.

Keywords— HDL – Hardware Description Language, MODEM – Modulator Demodulator, CODEC – Coding Decoding, Wi-Fi – Wireless internet Fidelity, I.T.U – International Telecom Unit, C.C.I.T.T – Consulting Committee for International Telegraph and Telephone, PRBS – Pseudo Random Binary Sequence, FPGA – Field Programmable Gate Array.

### I. INTRODUCTION

In Advanced Modern Hi-tech Data Communication & Network Engineering world , Parallel Network Data

Processing and controlling, Computing plays vital role in many electronic Data communication Computing and network engineering & IT products. Due to this I Designed Multichannel PRBS CODEC for transmission and reception of data processing through parallel computing of different channel baud-rate data speed of different channel frequencies. This is an 128 bit PRBS CODEC – generates multiple carrier waves modulates and demodulates with orginal base band data input signal of different channel frequency spectrum – simply spreading de-spreading the data. This codec is mainly suit for multiple baud rate frequency speed MODEM's, NIC's , Wi-FI routers. This is an heart of these products for computing data through big networking stations /servers. This is an high speed application product.

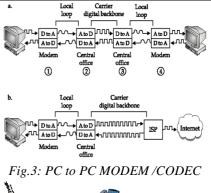

MODEM A. Basically "A modem (modulator*demodulator*) is a device that modulates an analog carrier signal to encode digital information, and also demodulates such a carrier signal to decode the transmitted information. So it is Data Conversion Equipment". The MODEM encode and decode the carrier signal using Pseudo random Binary Sequence(PRBS) Pattern Codes of Different Pattern sequences 2e<sup>7</sup>-1,2e<sup>10-</sup>1, 2e<sup>15-</sup>1,  $2e^{23-1}$ ,  $2e^{31-1}$ ,  $2e^{48-1}$ ,  $2e^{52-1}$ ,  $2e^{64-1}$ ,  $2e^{128}-1$ , and generation of ultra high speed frequencies. The goal is to produce a signal that can be transmitted easily and decoded to reproduce the original digital data. Modems are generally classified by the amount of data they can send in a given unit of time, usually expressed in terms of bits per second (bit/s, or bps), bytes/frames/super frames /very long word super frames/super very long word frames/packets of data rate. These signals can be

transmitted over telephone lines and demodulated by another modem at the receiver side to recover the digital data.

B. Modem, short for modulator-demodulator is an electronic device that converts a computer's digital signals into specific frequencies to travel over telephone or cable television lines. At the destination, the receiving modem demodulates the frequencies back into digital data. Computers use modems to communicate with one another over a network.

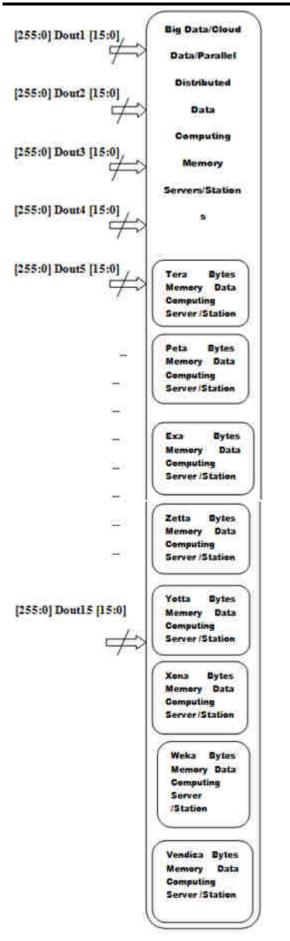

C. The wireless PRBS MODEM basically Designed for Encrypt and Decrypt Digital Data packets through wireless bus communication channel protocols of different broadband frequency spectrum for multiuser communication, the Wireless PRBS MODEM consists of Multichannel Encoder and Decoder and Wireless Channel Register Bus. This Wireless PRBS MODEM Support Data Speed In terms of Mega ,Giga, Tera, Peta, Exa, Zetta, Yotta, Xona, Weka, Vendica Bits Per second through Data Channel Bus.

D. The Wireless PRBS MODEM Chip Supports all 3G,4G,5G,6G wireless Computing applications.

E. At the source, modulation techniques are used to convert digital data (0's and 1's) into analog form for transmission across the channel. At the destination, the received analog signal is converted to digital data via demodulation. This is a simplified explanation of how a modem works, and there are other issues that require attention; such as channel impairments, encryption, error detection/correction, data compression, modulation, handshake negotiation, and echo cancellation.

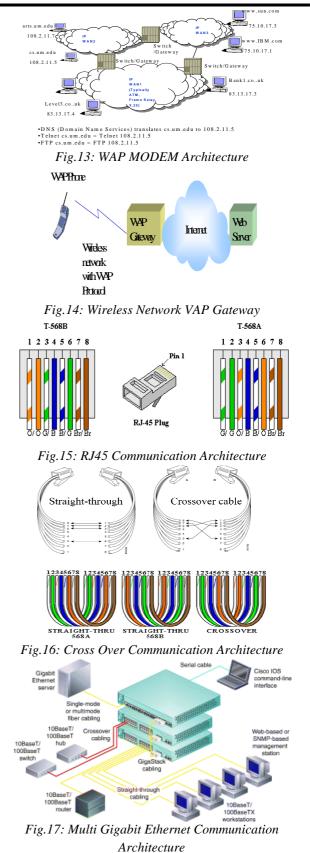

### II. BASIC MODEM ARCHITECTURES

#### Fig.1:Telephone MODEM Architecture

Fig.2: Internet MODEM Architecture

Fig.4: Telephone-PC MODEM Architecture

Fig.5: Internet-PC MODEM Architecture

Fig.6: Mobile-Mobile Service Architecture

Fig.7: Fixed Wireless Architecture

Fig. 10: Architecture of WAP Gateway

Fig.11: Internet Network Architecture

Fig.12: Wireless WEB Architecture

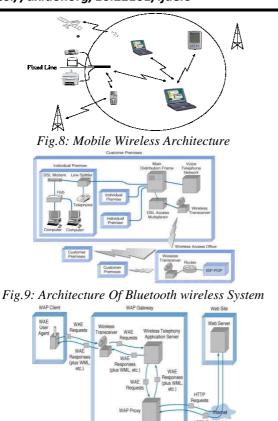

2(A). Architecture Description: The Diagrams Above represents different Hi-tech MODEM Communication Architectures based on the Priority Levels and Data Communication Capacity, these are Basic Telephone wire

and wireless MODEM, Internet MODEM, PC-PC, Telephone-to-PC MODEM, Mobile to Mobile, Consumer Mobile MODEM, MODEM Server, Bluetooth, Internet, WAP, Wireless Web Data Network, Fixed, Mobile wireless, WAP MODEM, Giga bit Ethernet MODEM , Server Computing Station Architectures. These above are widely used for LAN, MAN, WAN Systems, Cloud Internet, Cluster, Parallel Distributed Network Computing Architectures. These are mainly used for parallel communication for number of multiple users and multiple applications for sharing large data processing and computing with out any data loss of Large Broad Frequency Band Spectrum of large wider frequency Bandwidth. Compared to above modems, I designed new top class generation Hi-tech Smart Wireless Computing PRBS MODEM Architecture of Different PRBS Carrier Frequency Patterns-2e<sup>7</sup>-1,2e<sup>10-</sup>1, 2e<sup>15-</sup>1, 2e<sup>23-</sup>1, 2e<sup>31-</sup>1, 2e<sup>48-</sup>1, 2e<sup>52-</sup>1, 2e<sup>64-</sup>1,2e<sup>128</sup>-1 PRBS Tapped Sequences for large multi user parallel communication and data computing. I'm Implemented the Wireless PRBS CODEC through HDL Design(Verilog and VHDL), Data Transfer rate in terms of tera, peta ,exa,zetta,Yotta,xona,weka,Vendica Baud rate(Bits per Second). The wireless PRBS CODEC Consists of Different Cross Bar Router Switches for reducing the data traffic loss of large wide bandwidth. This is simply parallel distributed computing technique at a time data processing and computing done on number of multiple users. The speed of data is more than the internet modem because it is purely synchronized with tera, peta, exa, zetta, Yotta, xona, weka, Vendica clock frequencies.

## III. Ultra High MULTI CLOCK FREQUENCY BAUD RATE MULTICHANNEL WIRELESS PRBS MODEM/CODEC DESIGN ARCHITECTURE OF DIFFERENT PRBS PATTERN SEQUENCES

PRBS Decryption Architecture

Fig.18: Multichannel Wireless PRBS MODEM Architecture

### IV. SIMULATION WAVE FORM RESULTS A. PRBS ENCODER

V. Multichannel CODEC / MODEM Bus Array Design for Large /Big Data Network Computing Centers/Stations /Cloud/Internet Computing Server

| International Journal of Advanced Engineering Research and Science | (IJAERS) | [Vol-3, Issue-9, Sept- 2016] |

|--------------------------------------------------------------------|----------|------------------------------|

| https://dx.doi.org/10.22161/ijaers                                 | ISSN: 2  | 2349-6495(P)   2456-1908(O)  |

#

B.RTL SCHEMATIC – Multichannel PRBS CODEC

A. Multichannel Multi Clock Frequency Baud Rate (Tera Peta Exa Zetta Yotta Xona Weka Vendica Hertz Clock Frequency Synchronized ) PRBS CODEC ASIC SOC I.P Core

B. Technology Schematic Layout

C. FPGA PLACED DESIGN REPORT

D. FPGA Routed Design Report

E. PIN OUT Report

|       | Here . | <br> |  |

|-------|--------|------|--|

| 177-2 | 127-   | <br> |  |

|       |        |      |  |

|       |        |      |  |

## F. CLOCK REPORT

|         | A state from the second | an Lippe Sense La Sense Lippe Sense Lippe |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|

| Steen . | No. in with Second style 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Berner i Brinner i Aberlinen /            |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                           |  |

## G. ADVANCED SYNTHESIS REPORT

Final Register Report: Macro Statistics # Registers : 259 Flip-Flops: 259 # Multiplexers: 32 1-bit 8-to-1 multiplexer: 17 11-bit 8-to-1 mux: 2 16-bit 8-to-1 multiplexer: 2 24-bit 8-to-1 multiplexer:2 32-bit 8-to-1 mux : 2 48-bit 8-to-1 multiplexer: 2 52bit 8-to-1 multiplexer: 2 64-bit 8-to-1 Mux: 2 8-bit 8-to-1 multiplexer: 1 # Xors: 16 1-bit xor2: 16# Registers: 76 Flip-Flops: 76 # Shift Registers : 12 11-bit shift register: 1 13bit shift register: 1 18-bit shift register: 1 21-bit shift register: 4 4-bit shift register: 1 5-bit shift register: 1 6-bit shift register: 1 7-bit shift register: 1 9-bit shift register: 1

## Final Report : Final Results

RTL Top Level Output File Name: prbscodecdes.ngr Top Level Output File Name: prbscodecdes Output Format : NGC Optimization Goal : Speed Keep Hierarchy: NODesign Statistics# IOs : 141 Cell Usage : # BELS : 293 # GND : 1 # INV : 1 LUT2:12 # LUT3 : 173# LUT3\_L : 1 # LUT4 # MUXF5:63 # MUXF6:25 # MUXF7: : 10 4 # MUXF8:2 # VCC:1 # FlipFlops/Latches : 181 # FDE : 21 # FDRE : 160 # Shift Registers : 16 # SRL16E: 12 # SRLC16E: 4 # Clock Buffers : 1 # BUFGP:1 # IO Buffers:20 # IBUF:11 # OBUF:9 Selected Device : Device utilization summary: 3s200tq144-5 Number of Slices: 167 out of 1920 8% Number of Slice Flip Flops:181 out of 3840 4% Number of 4 input LUTs: 213 out of 5% 3840 Number used as logic: 197 Number used as Shift registers: 16 Number of IOs: 141 Number of bonded IOBs: 21 out of 97 21% Number of GCLKs: 1 out 8 12% of

Multiclock Multichannel PRBS CODEC

HDL SYNTHESIS REPORT Macro Statistics Registers : 160 1-bit register: 88 11-bit register : 8 128-bit register: 8 16-bit register : 8 24-bit register: 8 32-bit register: 8 48-bit register: 8 52-bit register: 8 64-bit register: 8 8-bit register : 8# Multiplexer : 1 1-bit 8-to-1 multiplexer: 1 # Xors : 18 1-bit xor2 : 18Summary: inferred 3152 D-type flip-flop(s). inferred 1 Multiplexer(s). Total REAL time to Xst completion: 7.00 secs Total CPU time to Xst completion: 6.88 secs

Advanced HDL Synthesis ReportMacro Statistics#Registers : 3136Flip-Flops : 3136# Multiplexers :11-bit 8-to-1 multiplexer: 1# Xors : 181-bit xor2 : 18

### AUTHOR BIBLIOGRAPHY

### Prof. P.N.V.M Sastry Currently working with a Capacity

of **Dean- IT EDA Software Industry CELL & R&D CELL & ECE** DEPARTMENT, He Did Master Degree In Science- **M.S Electronics**, Under Department Of Sciences, College Of Science & Technology

AU -1998.Did PG Diploma In V.L.S.I Design ,I.S.O.U.K.A.S Certified From V3 Logic Pvt Ltd, Bangalore-2001, Did M.Tech (ECE) From I.A.S.E Deemed University-2005. Currently Pursuing (Ph.D)-E.C.E(V.L.S.I), J.N.T.U Hyderabad -2012, Over Past 17 years of Rich Professional Experience with Reputed IT Software Industrial MNC's, Corporate –CYIENT (INFOTECH), ISITECH as a world top keen IT Industrial Software Specialist – World Top Software Engineering Team Leader(Level 6) Eng-Eng- HCM Electronics Vertical & Sr. Program Manager – EDS,BT,NON BT Embedded Software ,Avionics & Automotive Hi-tech Software Engineering Verticals &

Departments & I/C M.F.G Hi-tech Eng.Software Vertical , Program Lead – Embedded & VLSI & Engineering Delivery Manager - IT Semiconductor Software Engineering Vertical ,at ISiTECH , also worked with Govt R&D, Industrial Organizations, Academic Institutions of Comparative Designations & Rolls . His Areas Of Interest are V.L.S.I -V.H.D.L, Veirilog H.D.L, A.S.I.C, F.P.G.A & Embedded Software Product Architectures Design & Coding Development .He mentored & Architecting Various Real Time, R&D, Industrial Projects/Products related to VLSI & Embedded System Software & Hardware.. His Key Achievements are Participated Various Top Class International IT MNC Delegates Board Meetings, I.T Software M.N.C Board Meetings(Tier1/2 Level MRM-V.P.C.O.O Level), Guided R&D ,Industrial , Academic Projects /Products -VLSI-ASIC, FPGA & Embedded & Embedded, V.L.S.I Software Project &/ Program Management & Also Coordinated Various In House & External IT Project Workshops & Trainings At CYIENT( INFOTECH) as a I/C- MFG Eng Software Vertical, Also Participated Various National R&D Workshops, FESTS, FDP's &Seminars. Recently He Published Various 40 International Journals of Reputed Journals and Conferences also Certified Conference Chairs - ,I.T.C. I.D.E.S- MC GRAWHILL EDUCATION-Chennai & and Published 4 Journals at IEEE Computer Society and &I.E.E.E & I.E.E.E -C.S.N.T.-Gwalior & Best Paper Award On behalf of Exa Hertz Wi-Fi Router A.S.I.C Paper at I.S.S.R.D-I.C.S.C.D SANDIEGO, U.S.A., Accepted Journal at High Reputed Journal -Mitteilungen-Klosternburg Weiner Strasse, AUSTRIA, Europe etc.), and also J.M.E.S.T - Germany . Judge for Various Paper Presentations like IEEE-CBIT, JBREC Conferences ,Workshops etc. Recently Invited me as a Reviewer of IEEE TENCON-16, Singapore.

## Dr. D.N Rao B.Tech, M.E, Ph.D, Dean R&D ,JBIET

earlier he worked as a principal of JBREC, Hyderabad. His carrier spans nearly three decades in the field of teaching, administration,R&D, and other diversified in-depth experience in academics and administration. He

has actively involved in organizing various conferences and workshops. He has published over 11 international journal papers out of his research work. He presented more than 15 research papers at various national and international conferences. He is Currently approved reviewer of IASTED International journals and conferences from the year 2006. He is also guiding the projects of PG/Ph.D students of various universities Dr.Vathsal Currently working as a Professor- Aero Dept.

I.A.R.E, earlier He Was Dean R&D JBIET, He Obtained PhD from I.I.S.C,Bangalore,also Did Post Doctoral Research in DFVLR,Germany and NASA Goddard Space Flight Centre,USA,and also he worked with

keen Designations Scientist E,F,G from Reputed Govt R&D Industry Organizations over past years and closely worked with Dr.A.P.J Abdul Kalam He Published lot of various national, international journals & conferences, He guiding 5 PhD Students from Various universities. He Got Prestigious awarded as a Noble Son of India.